# **Developing Efficient Graphics Software: The Yin and Yang of Graphics**

## A SIGGRAPH 2000 Course

## **Course Organizer**

Keith Cok SGI

## **Course Speakers**

Keith Cok Roger Corron Bob Kuehne Thomas True SGI

## **Abstract**

A common misconception in modern computing is that to make slow software work more quickly, you need a bigger and faster computer. This approach is expensive and often unworkable. A more feasible and cost-effective approach to improving software performance is to measure the current software performance, and then optimize the software to meet the anticipated graphics and system performance. This course discusses the techniques and principles involved in this approach to application development and optimization with particular emphasis on practical software development.

The course begins with a general discussion of the interaction between CPUs, bus, memory, and graphics subsystem, which provides the background necessary to understand the techniques of software optimization. After this discussion of architecture fundamentals, we present the methods used to detect performance bottlenecks and measure graphics and system performance. Next, we discuss some general optimization techniques for the C and C++ languages. Finally, we give an overview of current application-level architectures and algorithms for reducing graphics and general system overhead.

## **Preface**

## **Course Schedule**

| 1:30 PM | Introduction                         |

|---------|--------------------------------------|

| 1:35 PM | General Performance Overview         |

| 2:05 PM | Software and System Performance      |

| 2:55 PM | Break                                |

| 3:10 PM | Profiling and Tuning Code            |

| 4:10 PM | Compiler and Language Considerations |

| 4:55 PM | Graphics Techniques and Algorithms   |

## **About the Speakers**

#### **Keith Cok**

MTS SGI

18201 Von Karman Ave., Suite 100, Irvine CA 92612

cok@sgi.com

Keith Cok is a Member of Technical Staff at SGI. He currently works with software developers in optimizing and differentiating their graphics applications. His primary interests include high-performance graphics, animation, scientific visualization, and simulation of natural phenomena. Prior to joining SGI, as an independent software developer, Keith wrote a particle-animation system used in several television and film shots. He also worked at TRW designing spacecraft and astronaut training simulators for NASA. Keith received a BS in Mathematics from Calvin College, Michigan, and an MS in Computer Science from Purdue University.

#### **Roger Corron**

MTS SGI

1 Cabot Road, Hudson, MA 01749

rc@hudson.sgi.com

Roger Corron is a Member of Technical Staff in SGI Custom Engineering, where he develops custom system solutions. Previously, Roger worked in SGI Applications Engineering assisting software developers to optimize their application graphics performance. Previous to SGI, he worked at Matra Datavision optimizing and porting solid modelling software to several different graphical APIs. His interests include low level graphics APIs and extracting maximum performance from computer systems. Roger received his BS in Electrical and Computer Engineering from Clarkson University.

#### **Bob Kuehne**

MTS SGI

39001 West Twelve Mile Road, Farmington Hills, MI 48331

rpk@sgi.com

Bob Kuehne is a Member of Technical Staff at SGI. He currently assists software developers and vendors in the CAD/CAE industries in developing products to most effectively utilize the underlying hardware. His interests include object-oriented graphics toolkits, software design methodologies, creative use of graphics hardware, and human/computer interaction techniques. Prior to joining SGI, he worked for Deneb Robotics developing software for virtual reality applications. Bob received his BS and MS in Mechanical Engineering from Iowa State University and performed research on assembly techniques in virtual environments.

#### **Thomas True**

MTS SGI

1600 Amphitheatre Pkwy., Mountain View, CA 94043

true@sgi.com

Thomas True is a Member of Technical Staff at SGI where he currently works assisting software developers in tuning their graphics applications. His primary areas of interest include low-level graphics system software, graphics APIs, user interaction, digital media, rendering, and animation. He received a BS in Computer Science from the Rochester Institute of Technology and an MS in Computer Science from Brown University where he completed his thesis on volume warping under the direction of Dr. John Hughes and Dr. Andries van Dam. He presented this research at IEEE Visualization '92. Prior to joining SGI, Thomas developed graphics system software at Digital Equipment Corporation.

## Acknowledgments

This course is based on our experience with real applications outside of SGI or in conjunction with partnerships through SGI Applications Consulting. We thank all of the graphics software developers and researchers who are pushing the envelope in graphics technology; without them there would be no content for this course.

We also thank our management, David Campbell, Brian Thatch, Janet Matsuda, and Keith Seto, for giving us the opportunity to develop this course and the course reviewers who gave us much needed feedback.

We gratefully acknowledge Alan Commike for his work on an ealier version of these course notes presented at SIGGRAPH99. We also gratefully acknowledge both Alan and Pam Thuman-Commike for their work with the proofreading, figures, and LaTeX formatting.

## **Course Resources On the Web**

The course notes and slides are available on the SGI web site:

http://www.sgi.com/events/siggraph00/gfxapps

## **Contents**

| Al | ostrac     | et                               |                                 | iii       |  |  |

|----|------------|----------------------------------|---------------------------------|-----------|--|--|

| Pr | Abo<br>Ack | rse Sche<br>ut the Sp<br>nowledg | edule                           | vi<br>vii |  |  |

| 1  | Cou        | rse Intr                         | roduction                       | 1         |  |  |

| 2  | Har        | dware /                          | Architecture and Performance    | 3         |  |  |

|    | 2.1        |                                  | uter System Hardware            |           |  |  |

|    | 2.1        | 2.1.1                            | Overview                        | _         |  |  |

|    |            | 2.1.2                            | Hardware Overview               | _         |  |  |

|    |            | 2.1.3                            | Computer System                 |           |  |  |

|    |            | 2.1.3                            | CPU                             |           |  |  |

|    |            | 2.1.5                            | Data Access Rates               | 6         |  |  |

|    |            | 2.1.6                            | Memory                          |           |  |  |

|    |            | 2.1.7                            | Graphics Hardware               |           |  |  |

|    |            | 2.1.7                            | Graphics Hardware Taxonomy      |           |  |  |

|    |            | 2.1.9                            | Bandwidth Limitations           |           |  |  |

|    |            |                                  | Larger Computing Architectures  |           |  |  |

|    | 2.2        |                                  |                                 | 23        |  |  |

|    | 2.2        | 2.2.1                            | ics Hardware Specifications     | 23        |  |  |

|    |            | 2.2.1                            | •                               |           |  |  |

|    |            |                                  | Graphics Performance Terms      |           |  |  |

|    | 2.2        | 2.2.3                            | Graphics Performance Techniques |           |  |  |

|    | 2.3        | Haruw                            | vare Conclusion                 | 23        |  |  |

| 3  | Gra        | Graphics Hardware Pipeline 27    |                                 |           |  |  |

|    | 3.1        | Introdu                          | <mark>uction</mark>             | 27        |  |  |

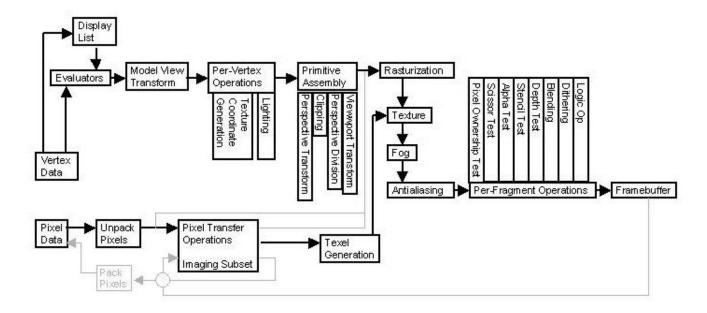

|    | 3.2        | Geome                            | etry Path                       | 28        |  |  |

|    |            | 3.2.1                            | Model-View Transform            |           |  |  |

|    |            | 3.2.2                            | Per-Vertex Operations           | 29        |  |  |

|    |            | 3.2.3                            | Texture Coordinate Generation   |           |  |  |

|    |            | 3.2.4                            | Lighting                        |           |  |  |

|    |            | 3.2.5                            | Primitive Assembly              |           |  |  |

|   |      | 3.2.6 Rasterization                                                   | 35         |

|---|------|-----------------------------------------------------------------------|------------|

|   |      | 3.2.7 Texture                                                         | 36         |

|   |      | 3.2.8 Fog                                                             | 36         |

|   |      | 3.2.9 Antialiasing                                                    | 37         |

|   |      | 3.2.10 Per-Fragment Operations                                        |            |

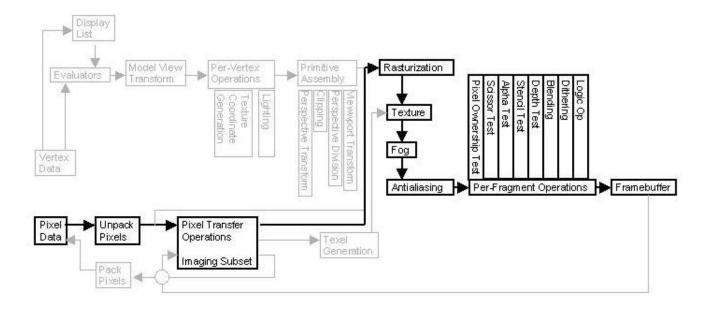

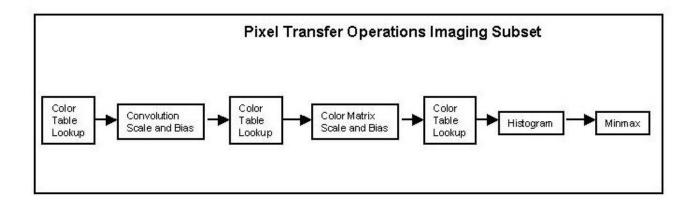

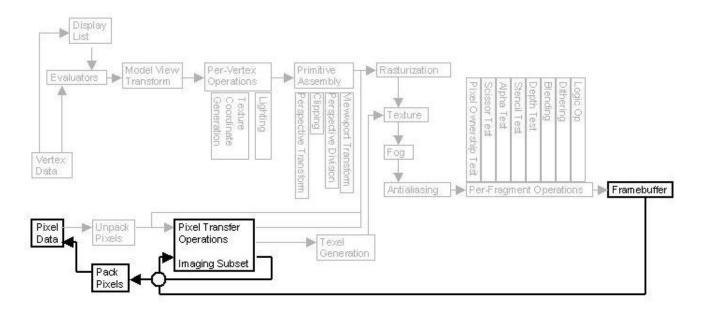

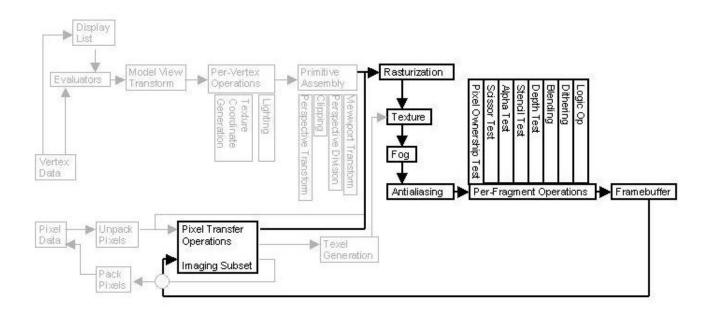

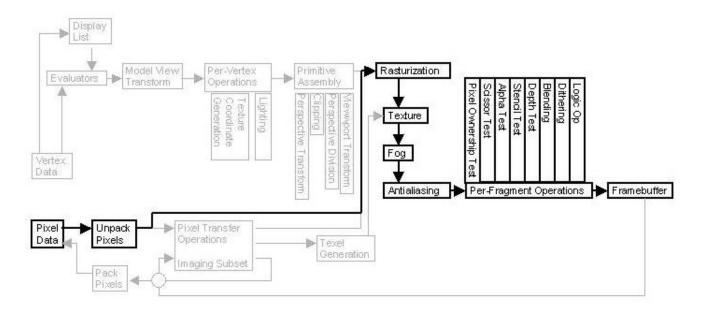

|   | 3.3  | Image Paths                                                           | 38         |

|   |      | 3.3.1 Draw Pixels                                                     | 39         |

|   |      | 3.3.2 Texture Path                                                    |            |

|   |      | 3.3.3 Read Pixels                                                     |            |

|   |      | 3.3.4 Copy Pixels                                                     |            |

|   |      | 3.3.5 Bitmap                                                          |            |

|   | 3.4  | Hardware Fast Paths                                                   |            |

|   | 3.5  | Conclusion                                                            |            |

|   |      |                                                                       |            |

| 4 | Soft | ware and System Performance 4                                         | 17         |

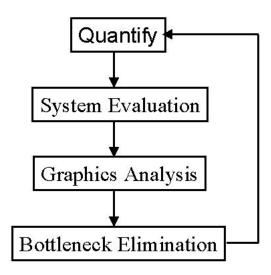

|   | 4.1  | Quantify: Characterize and Compare                                    | 17         |

|   |      | 4.1.1 Characterize Application                                        | <b>l</b> 7 |

|   |      | 4.1.2 Compare Results                                                 | 50         |

|   | 4.2  | Examine the System Configuration                                      | 50         |

|   |      | 4.2.1 Resources                                                       | 50         |

|   |      | 4.2.2 Configuration                                                   | 51         |

|   | 4.3  | Graphics Analysis                                                     | 53         |

|   |      | 4.3.1 Ideal Performance                                               | 54         |

|   |      | 4.3.2 CPU-Bound                                                       | 54         |

|   |      | 4.3.3 Graphics-Bound                                                  | 54         |

|   |      | 4.3.4 Architectural Considerations                                    | 55         |

|   |      | 4.3.5 Simple Techniques for Determining CPU-Bound or Graphics-Bound 5 | 57         |

|   | 4.4  | Bottleneck Elimination                                                | 57         |

|   |      | 4.4.1 Graphics                                                        | 59         |

|   |      | 4.4.2 Code and Language                                               |            |

|   |      | 4.4.3 Memory                                                          | 54         |

|   |      | 4.4.4 CPU                                                             | 55         |

|   |      | 4.4.5 Disk                                                            | 55         |

|   | 4.5  | Use System Tools to Look Deeper                                       | 55         |

|   |      | 4.5.1 Graphics API Level                                              | 55         |

|   |      | 4.5.2 Application Level                                               | 56         |

|   |      | 4.5.3 System Level                                                    | 56         |

|   | 4.6  | Conclusion                                                            | 59         |

|   |      |                                                                       |            |

| 5 |      |                                                                       | 71         |

|   | 5.1  | Why Profile Software?                                                 |            |

|   | 5.2  | System and Software Interaction                                       |            |

|   | 5.3  | Software Profiling                                                    |            |

|   |      | 5.3.1 Basic Block Profiling                                           |            |

|   |      | 5.3.2 PC Sample Profiling                                             |            |

|   | 5.4  | Conclusion                                                            | 15         |

| 6  | Con             | ipiler a | nd Language Issues                                         | 77  |  |  |  |  |

|----|-----------------|----------|------------------------------------------------------------|-----|--|--|--|--|

|    | 6.1             |          |                                                            |     |  |  |  |  |

|    | 6.2             | 32-bit   | and 64-bit Code                                            | 78  |  |  |  |  |

|    | 6.3             | User N   | Memory Management                                          | 79  |  |  |  |  |

|    | 6.4             | C Lang   | guage Considerations                                       | 80  |  |  |  |  |

|    |                 | 6.4.1    | Data Structures                                            | 80  |  |  |  |  |

|    |                 | 6.4.2    | Data Packing and Memory Alignment                          | 81  |  |  |  |  |

|    |                 | 6.4.3    | Source Code Organization                                   | 81  |  |  |  |  |

|    |                 | 6.4.4    | Unrolling Loop Structures                                  | 83  |  |  |  |  |

|    |                 | 6.4.5    | Arrays                                                     | 84  |  |  |  |  |

|    |                 | 6.4.6    | Inlining and Macros                                        | 84  |  |  |  |  |

|    |                 | 6.4.7    | Temporary Variables                                        | 84  |  |  |  |  |

|    |                 | 6.4.8    | Pointer Aliasing                                           | 85  |  |  |  |  |

|    | 6.5             | C++ L    | anguage Considerations                                     | 86  |  |  |  |  |

|    |                 | 6.5.1    | General C++ Issues                                         | 86  |  |  |  |  |

|    |                 | 6.5.2    | Virtual Function Tables                                    | 87  |  |  |  |  |

|    |                 | 6.5.3    | Exception Handling                                         | 87  |  |  |  |  |

|    |                 | 6.5.4    | Templates                                                  | 88  |  |  |  |  |

| 7  | Cro             | nhice Te | echniques and Algorithms                                   | 89  |  |  |  |  |

| ′  | 7.1             | -        | action                                                     |     |  |  |  |  |

|    | 7.1             |          | S                                                          |     |  |  |  |  |

|    | 1.2             | 7.2.1    | Caching                                                    |     |  |  |  |  |

|    |                 | 7.2.1    | Culling                                                    |     |  |  |  |  |

|    |                 | 7.2.3    | Application-specific Heuristics and Combinations of Idioms |     |  |  |  |  |

|    |                 | 7.2.3    | Level of Detail                                            | 95  |  |  |  |  |

|    | 7.3             |          | ation Architectures                                        | 99  |  |  |  |  |

|    | 1.5             | 7.3.1    | Multithreading                                             |     |  |  |  |  |

|    |                 | 7.3.2    | Frame-Rate Quantization                                    |     |  |  |  |  |

|    |                 | 7.3.3    | Memory vs. Time vs. Quality Trade-Offs                     |     |  |  |  |  |

|    |                 | 7.3.4    | Scene Graphs                                               |     |  |  |  |  |

|    |                 | 7.5.4    | Seene Graphs                                               | 103 |  |  |  |  |

| Co | onclus          | sion     |                                                            | 105 |  |  |  |  |

| Gl | ossar           | y        |                                                            | 107 |  |  |  |  |

|    | Bibliography 11 |          |                                                            |     |  |  |  |  |

| וע | SHUSI           | apiij    |                                                            |     |  |  |  |  |

## **List of Figures**

| 2.1  | Abstract computer system fabric                              | 5  |

|------|--------------------------------------------------------------|----|

| 2.2  | Abstract CPU                                                 | 6  |

| 2.3  | Data latencies and capacities                                | 6  |

| 2.4  | Virtual memory mapping                                       | 8  |

| 2.5  | Cache line structure.                                        | 9  |

| 2.6  | Register data request flowchart                              | 10 |

| 2.7  |                                                              | 12 |

| 2.8  | Graphics hardware pipeline and taxonomy                      | 13 |

| 2.9  | System interconnection architectures.                        | 16 |

| 2.10 | SSI Tiling Configuration                                     | 17 |

| 2.11 | COW Tiling Configuration                                     | 18 |

| 2.12 | Tiling techniques                                            | 23 |

|      |                                                              | •  |

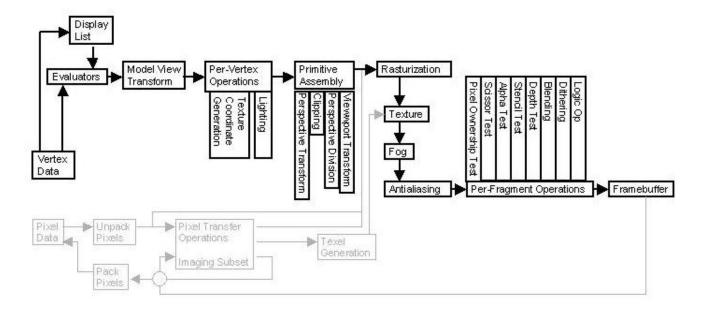

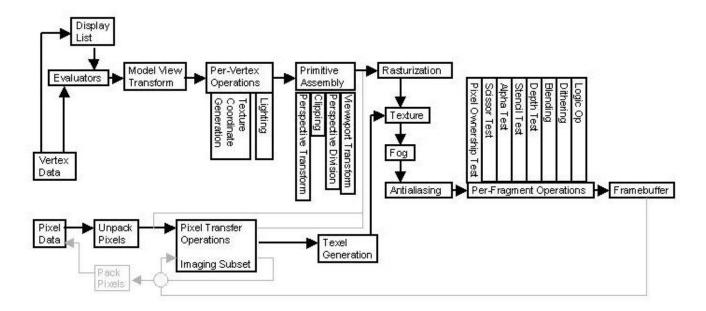

| 3.1  | Graphics Pipeline.                                           |    |

| 3.2  | 3D Path no Texture                                           |    |

| 3.3  | 3D Path with Texture.                                        | 39 |

| 3.4  | 2D Draw Pixels Path                                          | 40 |

| 3.5  |                                                              | 41 |

| 3.6  |                                                              | 42 |

| 3.7  | 2D Read Pixels Path                                          | 43 |

| 3.8  | 2D Copy Pixels Path                                          | 43 |

| 3.9  | 2D Bitmap Path                                               | 44 |

| 4.1  | A Four Step Process.                                         | 48 |

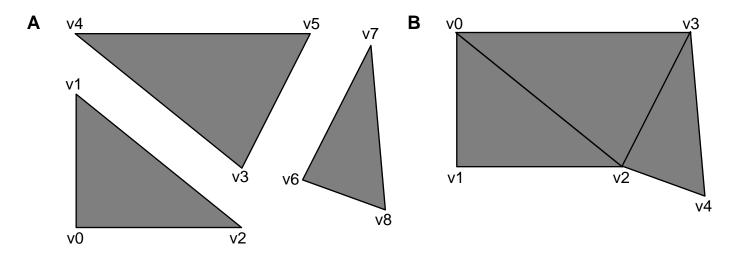

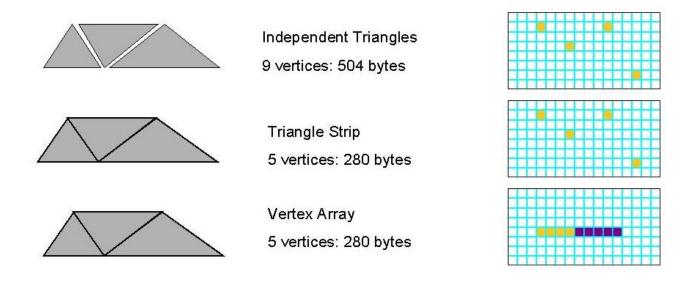

| 4.2  | Comparison of triangle and triangle strip data requirements. | 49 |

| 4.3  | The GTXR-D graphics subsystem.                               | 55 |

| 4.4  | The GTX-RD graphics subsystem.                               |    |

| 4.5  | The GT-XRD graphics subsystem.                               |    |

| 4.6  | Graphics performance analysis procedure                      |    |

| 4.7  | API Call Overhead.                                           |    |

| 4.8  | Memory Bandwidth and Fragmentation.                          |    |

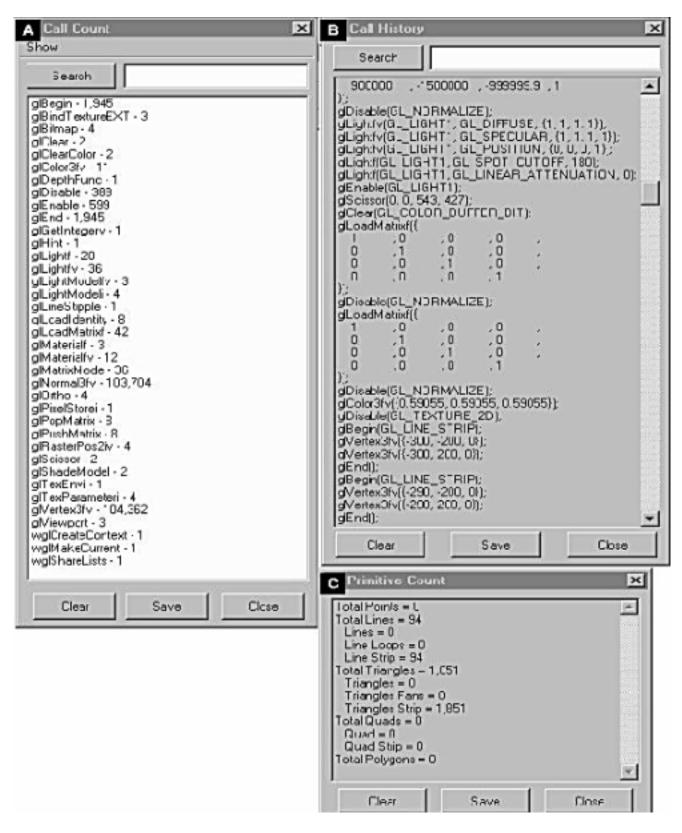

| 4.9  | Graphics API tracing tool example.                           |    |

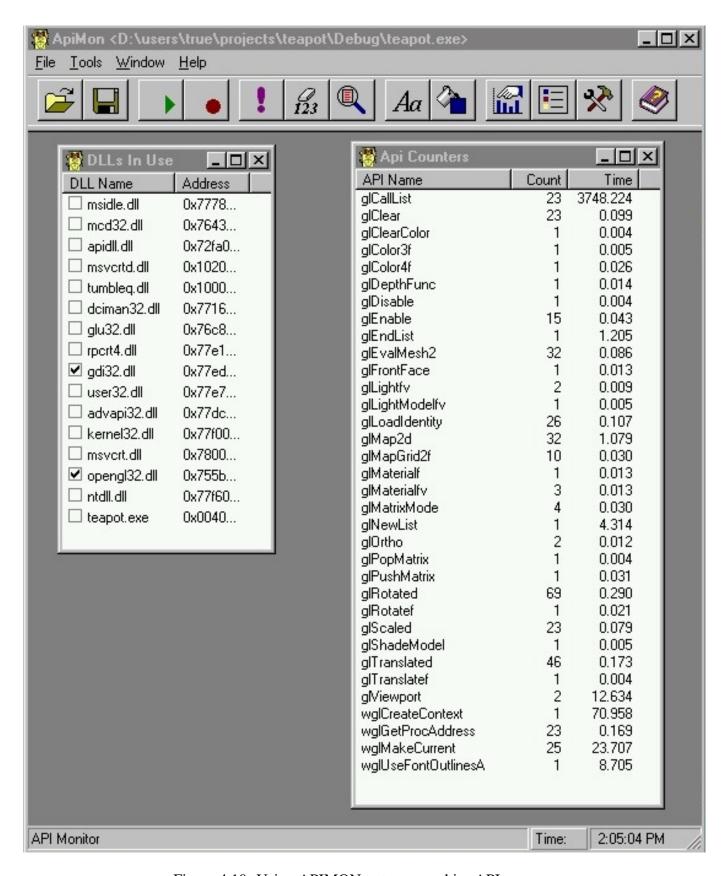

|      | APIMON tracing tool example                                  |    |

| 4.10 | Artivion tracing tool example                                | UC |

| 5.1  | The steps performed during code profiling                    | 73 |

| 5.2  |                                                              | 73 |

| 5.3  | Results of code profiling                                    | 74 |

| 5.4 | Profile comparison on an Intel CPU                        | 74 |

|-----|-----------------------------------------------------------|----|

| 5.5 | Example PC sampling profile                               | 76 |

| 6.1 | Example of how data structure choice affects performance  | 80 |

| 6.2 | Example of how data structure packing affects memory size | 82 |

| 6.3 | Loop unrolling example                                    | 83 |

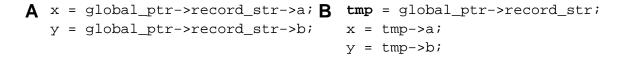

| 6.4 | Optimization using temporary variables                    | 84 |

| 6.5 | Optimization using temporary variables within a function. | 85 |

| 6.6 | Example of pointer aliasing.                              | 86 |

## **List of Tables**

| 6.1 | Effect of optimization o | the Dhrystone benchmark. |  | 78 |

|-----|--------------------------|--------------------------|--|----|

|-----|--------------------------|--------------------------|--|----|

## **Section 1**

## **Course Introduction**

This course was developed for software graphics developers interested in developing interactive graphics applications that perform well. The course is not targeted at a specific class of graphics applications, such as visual simulation or CAD, but instead focuses on the general elements required for highly interactive 2D and 3D applications. In this course, you will learn how to:

- Identify application and computer hardware interaction

- Introduce techniques to quantify and optimize that interaction

- Create and structure applications efficiently

- Balance the utilization of software and hardware system components

The course begins by discussing hardware systems, including CPU, bus, and memory. The course then covers graphics devices, theoretical and realized throughput, graphics hardware categorization, hardware bottlenecks, graphics performance characterization, and techniques to improve performance. Next, the course discusses application profile analysis, and compiler and language performance issues (for C and C++). The course then progresses into a discussion of application graphics rendering strategies, frameworks, and concepts for high-performance interactive applications.

This course is founded on the premise that creating high-performance graphics applications is a difficult problem that can be addressed through careful thought given to hardware and software systems interaction. The course presents a variety of techniques and methodologies for developing, analyzing, and optimizing graphics applications performance.

## **Section 2**

## **Hardware Architecture and Performance**

## 2.1 Computer System Hardware

This section describes application hardware interaction issues, specifically those encountered when writing graphics applications. The hardware upon which an application runs can vary dramatically from system to system and vendor to vendor. Understanding some of the design issues involved with hardware systems can improve understanding of application hardware utilization. Tuning the application based on this understanding can, in turn, lead to overall application and graphics performance improvements through more effective use of hardware resources.

### 2.1.1 Overview

To understand why a graphics application is slow, you must first determine if the graphics are actually slow, or if the bottleneck lies elsewhere in the system. In either case, it's important to understand both the code and the target system on which the code is running, how the two interact, and the strengths and weaknesses of the system.

In this section, hardware, software, and their interaction are discussed with a specific emphasis on graphics applications and graphics hardware. Also discussed is the process an application goes through to get data to the graphics hardware. Additionally, concepts for maximizing application performance are discussed throughout this section.

#### **Bottlenecks and Yin & Yang**

A key discussion throughout this portion of the course is that of *bottlenecks*. The word bottleneck refers to a point in an application that is the limiting factor in overall performance; that is, the point in an application that is the slowest and thus constrains its performance. A bottleneck in an application can be thought of much like its physical namesake, with the application trying to pour the bottle's contents (the application data and work) through the bottleneck (the slowest function, method, or subsystem). Improving performance for any application involves identifying and eliminating bottlenecks. Note, however, that once one bottleneck is removed, another often appears. For example, if in a room full of people, sorted by height, the tallest person is removed, there will still be another person remaining who is tallest. From this analogy, it would appear that an application developer's work is never done.

Fortunately, the goal in tuning an application is not to merely eliminate bottlenecks. The goal in tuning an application is to cause an application's work to be spread efficiently across all the component hardware

and subsystems upon which it runs. A useful metaphor for this balance (and diversion from the topic of computer hardware) is the Chinese concept of yin and yang. Quoting from the Skeptics Dictionary (http://skepdic.com/yinyang.html):

According to traditional Chinese philosophy, yin and yang are the two primal cosmic principles of the universe. Yin (Mandarin for moon) is the passive, female principle. Yang (Mandarin for sun) is the active, masculine principle. According to legend, the Chinese emperor Fu Hsi claimed that the best state for everything in the universe is a state of harmony represented by a balance of yin and yang.

Although the ideas behind yin and yang do not map exactly to the main goal of application tuning, the basic concept of balance is key. If the re-purposing of this ancient Chinese philosophy can be forgiven, the goal in tuning an application is to obtain harmony, a state of blissful balancing of application load across the hardware provided in a computer. Throughout the remainder of this course, the yin/yang symbol appears in the margin to denote a section of interest that discusses harmonious application balance. A consequence of trying to obtain balanced hardware usage is the need to understand how that hardware operates so that an application can best take advantage of it.

Another icon used throughout the course is the winged foot of Mercury. This icon indicates an explicit performance hint or suggestion. The goal of this course is not, however, to give explicit hints, but to encourage overall understanding of an application and its interaction with the computer on which it runs. Therefore, scanning the course for these icons and following the hint without understanding the surrounding concepts and content will not be of much value. Furthermore, much larger performance increases can be obtained by implementing the concept, as opposed to implementing a specific suggestion. Take care to understand why a particular suggestion is given, where it will work, and most importantly, the context of the section surrounding the suggestion.

#### 2.1.2 Hardware Overview

Computer systems are constructed from a wide variety of components, each with its own characteristics. Aside from the obvious differences in core functionality among network interfaces, hard disk drives, graphics accelerators, and serial port controllers are the less obvious differences in the way these systems respond to input.

Some systems are said to *block* when input or output is requested. Blocking is the process of preventing the controlling program from proceeding in its current thread of execution until the device being communicated with its finished with its operation. Blocking operation of a system is also known as *synchronous operation*. Other devices operate asynchronously, or in a non-blocking mode, allowing data to be queried and program execution to continue regardless of the result of the query.

Other differences among devices are the rates at which they can communicate data back to the host, the latency involved in these data transfers, and how various buffers and caches are used to mitigate the effects of these differences among devices. Subsequent sections discuss these issues in more detail.

## 2.1.3 Computer System

An abstract computer system is described in this section to motivate thinking about how a system is structured and how a program interacts with this hardware. This abstract computer system has components found on most computer systems, but it is not intended to represent any actual system. Any similarities to real computer systems, living or dead, are purely coincidental.

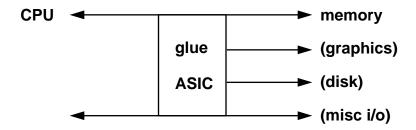

The architecture of a specific computer system is important to consider when designing software for that system. Specifically, it's important to consider which subsystems an application interacts with, and how that interaction occurs. There are several distinct systems on a computer, each using some interconnect fabric or "glue," (shown as a single block in Figure ??) to communicate with each other. Understanding this fabric and where devices live on this fabric is extremely important in determining where application bottlenecks occur, and avoiding bottlenecks when designing new software systems.

Figure 2.1: An abstract computer system fabric.

Interconnect fabrics vary dramatically from system to system. On low-end systems, the fabric is often a bus on which all devices share access through some hardware arbitration mechanism. The fabric can be a point-to-point peering connection, which allows individual devices to communicate with preallocated guaranteed-bandwidth. In still other fabrics, some systems might live on a bus, while others in that system live on a peered interface. The differences in application performance among these types of systems can be dramatic depending on how an application uses various components.

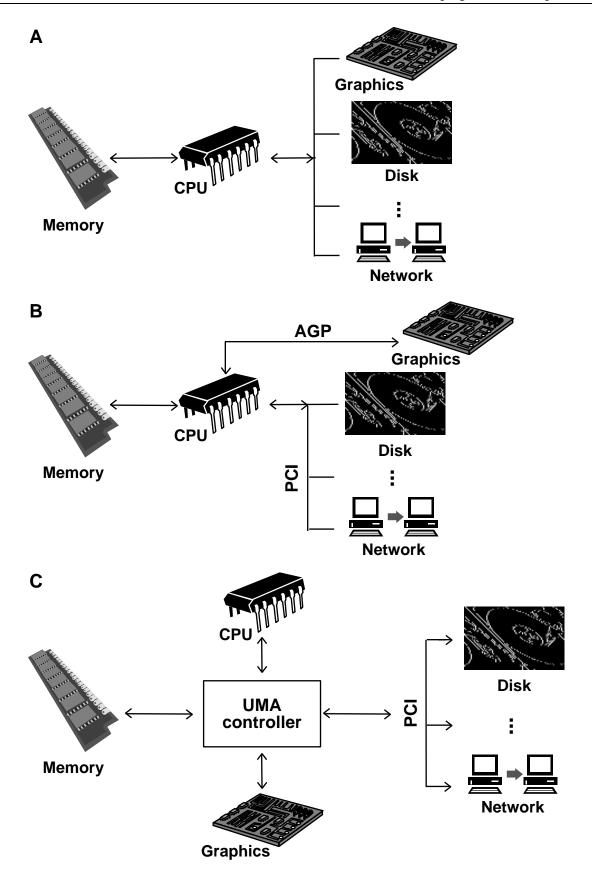

Because the focus of this course is on writing graphics applications, understanding the specifics of how graphics hardware interfaces with CPU, memory, and disk is of special importance. A diverse mix of computer systems exists on which an application might be run. This diversity ranges from systems with a shared-bus (PCI) with local texture and framebuffer, to systems with a dedicated bus to the graphics (AGP) with some local texture cache, some main memory texture cache, and local framebuffer, to systems on a dedicated bus with all texture and framebuffer allocated from main memory (SGI O2). Each of these architectures has certain advantages and disadvantages, but an application cannot be expected to fully realize the performance of these platforms without consideration of the differences among them.

As a concrete example of these differences, let's examine shared-bus systems. Graphics systems using a shared-bus architecture share bandwidth with other devices on that bus. This sharing impacts applications attempting to transfer large amounts of data to or from the graphics pipe while other devices are using the bus. Large texture downloads, framebuffer readbacks, or other high-bandwidth uses of the graphics hardware are likely to encounter bottlenecks as other parts of the system utilize the bus. (A complete description of the different types of graphics accelerator hardware strategies appears in later sections of the course notes.) Regardless of the type of system being used, the key to high-performance applications is to fully utilize the entire system, balancing the workload among all the components needed so that more application work can be performed more quickly.

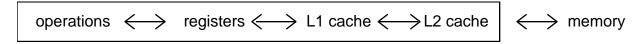

#### 2.1.4 CPU

Figure 2.2 depicts a simplistic CPU to illustrate the lengthy path that application data must travel before it is useful. In this figure, main memory lives on the far side of all the caches, and data must be successively cached down to the registers before it can be operated on by the CPU. This means that keeping often-used data localized in memory is a very good idea, as it can improve cache efficiencies dramatically. In fact,

the premise behind caches is that data near the current data being operated upon is much more likely to be needed next. This design criterion means that data locality affects performance, because access to cache memory is significantly faster than to main memory.

Figure 2.2: Abstract CPU.

Application data transfers to the graphics hardware that avoid pushing data through the CPU can significantly improve performance. Graphics structures such as OpenGL display lists (other graphics APIs have other nomenclature for this concept) can often be pre-compiled into a state such that a glCallList() simply transfers the display list directly from main memory to the graphics hardware, using a technique such as direct memory access. This technique allows large amounts of graphics data to be rendered without any complex calculations occurring on that data at run time.

#### 2.1.5 Data Access Rates

Two other key measures of performance relevant to discussing computer hardware are *bandwidth* and *latency*. Bandwidth is the amount of data per time unit that can be transmitted to a device. Latency is the amount of time it takes to fully transfer a single unit of data to a device. The difference between the two is quite clear, but the interaction between the two is not.

Different hardware systems have often very different bandwidth abilities in different portions of a system. For example, the 33-MHz, 32-bit PCI bus has a theoretical bandwidth of 133 MB/s, calculated simply by multiplying 33M cycles/second \* (32 bits/cycle or 4 bytes/cycle) to yield 133M bytes/second. The 66-MHz, 32-bit AGP graphics bus has a theoretical bandwidth of either 264 MB/s (or 528 MB/s depending on whether or not data transfer happens on both edges of the clock cycle). Other systems have vastly greater bandwidths.

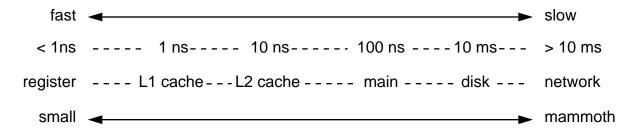

Latency can be measured between many points in a system, so it is helpful to know where latency is important to an application. Profiling an application can yield insight into where critical latencies are encountered. Profiling will be discussed in later sections, but the key result of profiling will show which routines take up the most time. These time-intensive routines can either be computationally complex, or be doing much simpler tasks which are latency critical. Learn to profile an application with an eye towards latency recognition. Latencies vary dramatically within a system. For example, network latencies can be on the order of many milliseconds (or even seconds), whereas latencies for data in L2 cache operate on the order of tens of nanoseconds (Figure 2.3).

Figure 2.3: Approximate data latencies and capacities of typical system components.

Now that a few typical latencies and bandwidths have been discussed, how do the two interact? When transferring data from one piece of hardware to another, both measures are important. Latency is most often a factor when many operations are being performed, each with a latency that is large relative to length of the overall operation. Latency is critical when accessing memory, for example, as the access times for portions of main memory are approximately an order of magnitude slower than those of cache memories.

A hypothetical graphics device is used to illustrate the effects that latencies can have on a running program. Assume that this system consists of a data source (memory) and a data sink (graphics) where the bandwidth between source and sink is 1 MB/s and the latency is 100 ms. The hypothetical application programming interface (API) in this example is a call that blocks (is synchronous) while downloading a texture. The transfer time for a 100-MB download of a texture (assuming no other delays in retrieving the data) will then take 100s. As the latency involved in transferring this texture is 100 ms or 0.1 second, then the overall time to transfer this texture is 100.1 seconds. However, if 100 1-MB textures are downloaded, the transfer time per texture is 1s, for a total of 100 seconds. Adding in the latency of 0.1 second per texture, we add a cumulative additional 10 seconds, thus bringing the total transfer time up 10% to 110 seconds total. A developer aware of this issue could design methodologies such as creating a large texture with many small sub-textures within it to avoid many small data transfers that could negatively impact performance. Though contrived, this example illustrates that latency can be an issue affecting application performance, and that developers must be aware of hardware latencies so their effects (the latencies, not the developers) can be minimized.

### **2.1.6 Memory**

Previous sections have described the effects of latencies and bandwidths on hypothetical activities. This section of the course discusses memory hierarchies and how applications interact with data within memory. This section describes how memory hierarchies work in general, but many details are beyond the scope of this course, such as instruction vs. data caches, details behind cache mappings (direct, n-way associative, etc.), translation look-aside buffers, and many others.

#### **Virtual Memory**

Most current operating systems work under a memory scheme known as *virtual memory*. Virtual memory is a method of managing memory that allows applications access to data storage space sized significantly larger than the amount of physical RAM in a system. Addressing schemes vary, but 32-bit applications can typically address >1 GB of memory when only a small fraction of that is physically available. Virtual memory systems perform this task through managing a list of active memory segments known as *pages*. For details behind this operation, and that of many computer systems, see *Principles of Computer Architecture* [41] or a good introductory computer architecture book for elaboration.

Pages of memory are blocks of *address space* of a fixed size. Memory address space is simply a hardware mapping of all available memory locations to a numbering scheme. A simplistic mapping for a 16-byte memory system might have valid memory addresses of 0x00 to 0x10. The size of pages of memory varies from system to system but is typically constant on a specific running system. However, many hardware systems allow the page size to be changed, some operating systems allow this to be changed dynamically as a tunable parameter. Knowing the page size and page boundary for the specific system on which an application is running can be very useful, as will be explained more fully in a moment. Specific page sizes and functions to retrieve page size and page boundary vary by operating system. Pages are

important structures to understand because they are used as the coarsest level of data caching that occurs in virtual memory systems.

As applications use memory and address space for code and data storage, more and more pages of that address space are allocated and used. Eventually, more pages are in use than are available in physical system RAM. At that point, the virtual memory manager decides to move some infrequently used pages from that application from main memory to disk. This process is known as paging. Each time a page of memory is requested, the memory manager checks if it already exists in main memory. If it does, no action is required; if it does not, the memory manager checks if there is space available in RAM for that page. If space is available in RAM for the needed page, no action is required, but if not, a page of resident data must be put to disk prior to writing the desired page from disk. Next, in all cases, the desired page is copied from disk, to the available page location in RAM. When an application pages, disk I/O occurs, thus impacting both the application and overall system performance. Because maintaining the integrity of a running application is essential, the paging process operates in a fairly resource-intensive fashion to ensure that data is properly preserved. Because of these constraints, keeping data in as few pages as possible is important to ensure high-performance applications. Applications that typically use very large datasets, which cause the system to page, may benefit from implementing its own data paging strategy. Application-specific paging can be written to be much more efficient than the general OS paging mechanism.

Figure 2.4 shows a hypothetical application with an address space ranging from page 0 to page n, and a system with many physical pages of RAM. In this example application, pages 0 - 9 are active, or have data of some sort stored in them by the application, and pages 0 and 1 are physically resident in RAM. For this example, the memory manager has decreed that only two pages can be used by the application, so any application data that resides on pages other than the two in RAM are paged to and from disk.

Figure 2.4: Virtual memory mapping active pages into RAM.

If the application in this example needs to retrieve vertex data from each of the 10 pages in use by the application, then each page must be cached into RAM. This process will likely require eight paging

operations, which can be quite expensive, given that disk access is several orders of magnitude slower than RAM access. However, if the application could rearrange data such that it all resided on one page, no paging by the virtual memory manager would be required, and access times for this data would improve dramatically. This is known as *data locality*, or the property of one piece of data residing "close" to another piece of data in memory. If data locality can be improved, by storing frequently-used data in adjcent memory, performance may improve as well. Understanding data access patterns is key to understanding and improving data locality.

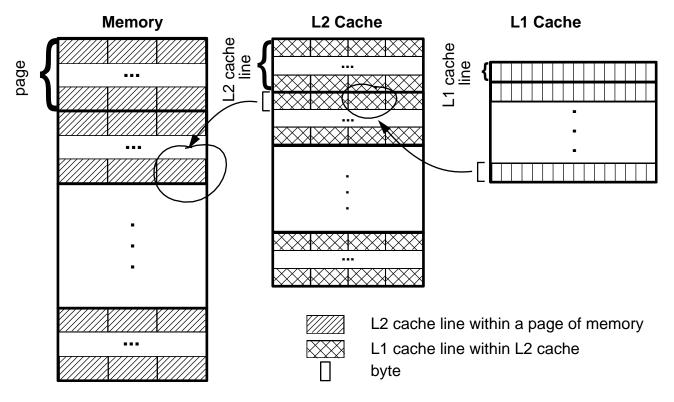

When data is resident on pages in main memory, it must then be transferred to the CPU (see Figure 2.2) in order for operations to be performed on it. The process by which data is copied from main memory into cache memory is similar to the process by which data is paged into main memory. As memory locations are required by the operating program, they must be copied ultimately into the registers. Figure 2.5 shows the data arrangement of cache lines in pages and both caches.

To get data to the registers, active data must first be cached into L2 and then L1 caches. Data is transferred from pages in main memory to L2 cache in chunks known as *cache lines*. A cache line is a linear block of address space of a system-dependent size. Level-2 (L2) caches are typically sized between 32-128 bytes in length. As data is required by the CPU, data from L2 cache must be copied into a faster level-1 (L1) cache, again of a system-dependent size, typically of around 32 bytes. Finally, the actual data required from within the L1 cache is copied into the registers, and operated upon by the CPU. This is the physical path through which data must flow to be able to be operated on by the CPU.

Figure 2.5: Cache line structure. Shown are pages of memory composed of multiple L2 cache lines; L2 cache composed of multiple L1 cache lines; and L1 cache composed of individual bytes.

The process by which requested data is copied into the registers is important because the consequences of its action are one of the primary factors limiting application performance. As data is needed by the CPU, controlling circuitry checks to see if that data is in the registers. If the data is not immediately available,

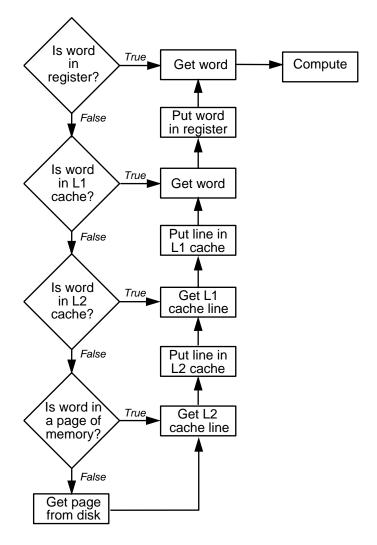

the controller checks the L1 cache for the data. If again not available, the controller checks the L2 cache. Finally, if the data is still not available, a cache line containing the required data is copied from a page in main memory (assuming that the page is already resident in RAM, and not paged to disk) and propagated through L2 and L1 cache, ultimately depositing the requested data in a register. This process is depicted in Figure 2.6, which shows the data request procedure as a flow chart.

Figure 2.6: Register data request flowchart.

Though this discussion of memory and how it works is straightforward, the relevance to application performance may not be immediately clear. *Data locality*, or packing frequently used data near other frequently used data in memory, is the ultimate point of any discussion of how memory works. Keeping data closer together keeps data in faster and faster memories in the memory hierarchy. Conversely, data that is widely dispersed in memory is accessed through slower layers in the memory hierarchy. The effects of data locality are best demonstrated through two examples.

In these examples, an operation is being performed in the CPU that requires 2 bytes of data, each in a register. The computer on which this operation is running has the following access times: L1 cache, 1 ns; L2 cache, 10 ns; main memory, 100 ns. These access times are the largest contributors to overall data access time. In the first example, the 2 bytes of data are resident on two different pages of memory, so for each data to be accessed, a cache line must be copied from main memory into the cache. Thus, to

access main memory, it takes 100 ns + the L2 cache access time (10 ns) + the L1 cache time (1 ns), or 111 ns for each data byte to be copied from main memory to a register. Therefore, for the first example, the total time to prepare memory for the operation to occur is 222 ns. Note that in this example, the two bytes are the data of interest, but complete L2 cache lines containing the bytes of interest are copied from main memory, and L1 cache lines containing the bytes are copied from L2 cache to L1 cache. Finally a word containing each byte of interest is copied to each register location.

In the second example, both data bytes live on the same page in memory and on the same L2 cache line (though far enough apart that they don't fit on the same L1 cache line). A much smaller time to set up this operation is needed than in the first example. Again, it takes 100 ns to access the main memory page to copy to L2 cache, 10 ns to access the L2 cache twice to copy each byte to a different L1 cache line, two 1-ns accesses to the L1 cache to load the registers. In this example, the total time to prepare the operation is 122 ns, which is nearly half the previous example's overall time. As these examples show, keeping data localized can clearly benefit application performance. Keep in mind this cache effect when designing graphics data structures to hold objects to be rendered, state information, visibility lists, etc. Some simple changes in data structure organization can possibly gain a few frames per second in the application frame rate.

Another example of how data locality can be of great advantage to a graphics application is through a graphics construct known as a *vertex array*. Vertex arrays allow graphics data to be efficiently utilized by the CPU for transformation, lighting, etc. This efficiency is primarily due to the fact that vertex arrays are arranged contiguously in memory, and therefore subsequent accesses to vertex data are likely to be found in a cache. For example, if a hypothetical L2 cache uses 128-byte lines, then four 32-bit floats can live on a single cache line, allowing fast access to each of them. However, because most applications do more than render flat-shaded triangles, these vertices will need normals too. If a large contiguous array is allocated in memory for the vertices, another for the normals, another for the color, and so on, it's possible that, due to the implementations of the L2 caches these arrays may overlap in cache, and still incur trips to main memory for access. A solution to this problem is the concept of interleaved vertex arrays. In this case, vertex, normal, and color data are arrayed one after another in memory; therefore, in a 128-byte cache line implementation, all three are quite likely to live in non-overlapping L2 cache at once, thus improving performance.

A number of techniques exist for mitigating the effects of cache on data access performance; however, these techniques are more adequately addressed in later sections of this course, which discuss language and code optimizations.

Understanding the path through which data must flow to get to the CPU is key because of the latencies involved in accessing data from various memory caches. Keeping data packed close together in memory ensures the likelihood of subsequent data accesses occurring from memory already resident in cache, and, therefore, the algorithms operating on that data will be much faster.

## 2.1.7 Graphics Hardware

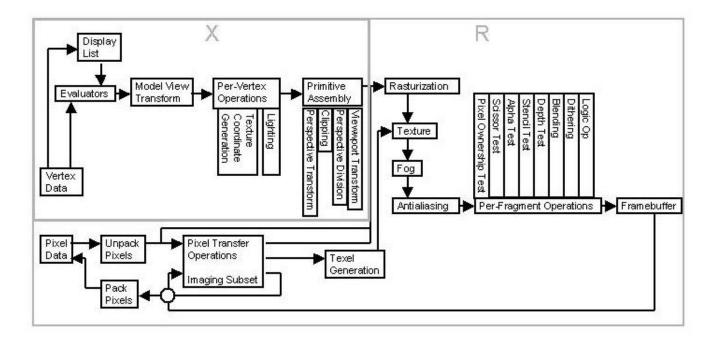

The graphics subsystem is responsible for the actual rendering and display of application data. The rendering process, also know as the *graphics pipeline*, is typically implemented as a combination of CPU-based software and dedicated graphics hardware. The hardware functionality within this subsystem and the physical connection between it and the other parts of a system play a large role in the overall performance of a graphics application. This section reviews the rendering pipeline, and describes how you can use special-purpose dedicated hardware to implement it, and the relative impact different hardware implementations have on overall application performance.

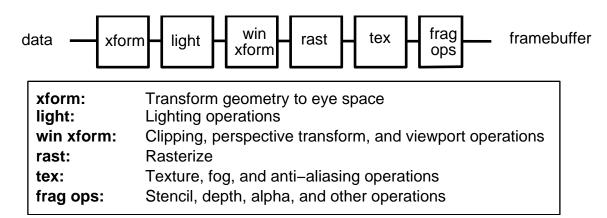

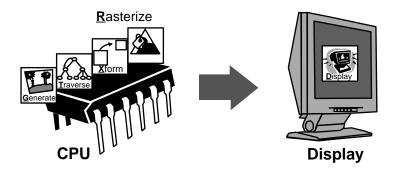

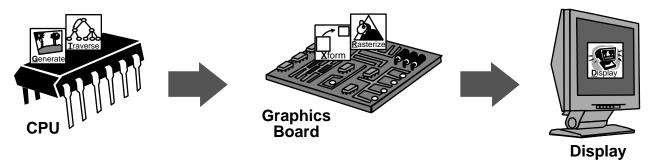

Figure 2.7: Graphics pipeline.

### **Graphics Pipeline**

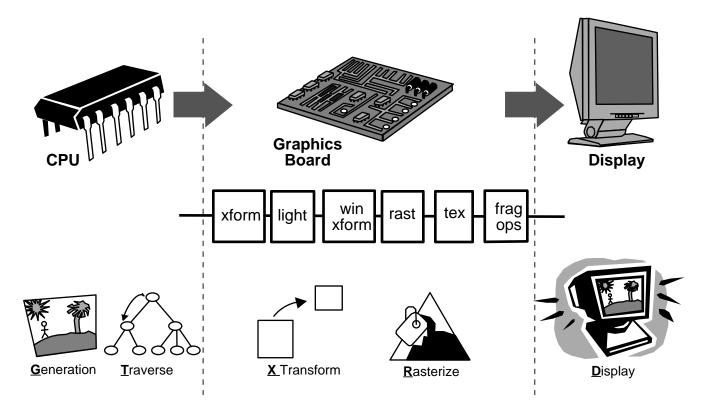

The process of rendering interactive graphics can best be described as a series of distinct operations performed on a set of input data. This data, often referred to as a *primitive*, typically takes the form of triangles, triangle strips, image data, points, and lines. Each primitive enters the process as a set of vertex data in a world coordinate system, and leaves as a set of pixels in the framebuffer. This set of stages, which performs this transformation, is known collectively as the graphics pipeline (Figure 2.7).

When implemented using special-purpose dedicated hardware, the graphics pipeline can conceptually be reduced to five basic stages[8].

**Generation** The process of creating the actual graphics data to be rendered, and organizing it into a graphics data structure. Generation includes all the work done by an application on the CPU prior to the point at which it's ready to render.

**Traversal** The process of walking through the internal graphics data structures and passing the appropriate data to the graphics API.

Typically, this stage of the rendering process is not implemented in dedicated hardware. Immediate mode graphics requires flexible traversal algorithms that are much easier to perform in software on the host CPU. Retained mode graphics, such as OpenGL display-lists, can be implemented in hardware and then are part of the traversal phase.

**Transformation** The process of mapping graphics primitives from world-space coordinates into eye-space, performing lighting and shading calculations, mapping the eye-space coordinates to clip-space, clipping these coordinates, and projecting the final result into screen-space.

Graphics subsystems with hardware support for this stage do not always accelerate all geometric operations. Often, there is a limited number of paths that are fully implemented in hardware. For example, some machines may only accelerate geometric operations involving one infinite light, others may not accelerate lights at all. Some hardware accelerators may have dedicated ASICs that transform geometric data faster for triangle strips of even lengths rather than odd (due to parallelism in the geometry engines). Understanding which operations in this portion of the graphics pipeline are performed in hardware, and to what degree, is critical for building fast graphics applications. These operations are known as *fast paths*. Determination of hardware fast paths is discussed in Sections 2.2.3 and 3.4.

Figure 2.8: Graphics hardware pipeline and taxonomy.

**Rasterization** The process of drawing the screen-space primitives into the framebuffer, performing screen-space shading, and per-pixel operations. Per-pixel operations performed in this phase include texture lookups and depth, alpha, and stencil tests. Following this stage in the pipeline, there remain only fragments, or pixels with a variety of associated data such as depth, color, alpha, and texture.

Any (or all) rasterization operations can be incorporated into hardware, but very frequently, only a limited subset actually are. Reasons for this limitation are many, including cost, complexity, chip (die) space, target market applicability, and CPU speed. Some hardware may accelerate textures only of certain formats (ABGR and not RGBA), whereas others may not accelerate texture at all, targeting instead markets such as CAD where texture is (as of yet, relatively) unimportant. It is important to know what is and is not implemented in hardware to construct a well-performing graphics application.

**Display** The scanning process that transfers pixel data in the framebuffer to the display monitor.

This stage is always implemented in dedicated hardware, which provides a constant refresh rate (for example, 60 Hz, 75 Hz).

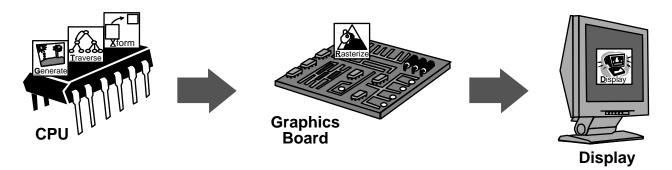

Figure 2.8 shows how these five stages overlay onto the original graphics pipeline. These five stages can be used to build a useful taxonomy that classifies graphics subsystems according to hardware implementation. This taxonomy, its mapping onto hardware, and consequent performance implications are the subject of the next section.

## 2.1.8 Graphics Hardware Taxonomy

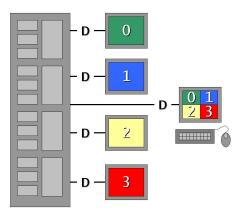

Graphics subsystems can be classified as one of four different types. Each type can be named using **G**, **T**, **X**, **R**, and **D** to represent the five stages of the graphics rendering pipeline. A dash represents the division between those stages performed in dedicated graphics hardware and those stages performed in software on the host CPU. The following classification scheme is used in subsequent sections to describe how different hardware implementations impact rendering performance.

- **GTXR-D** The sole function of a GTXR-D type graphics subsystem is to regularly update the screen at the set refresh frequency by scanning the pixel values from video memory to a display monitor. All other rendering stages are performed on the host CPU.

- **GTX-RD** GTX-RD type graphics subsystems have a rendering engine that implements the scan conversion of screen-space objects (points, lines, and polygons) into video memory and performs screen-space shading and other pixel operations (depth testing, stencil testing, etc.). Transformation and lighting are still performed on the host CPU.

- **GT-XRD** GT-XRD type graphics subsystems go one step beyond GTX-RD with the addition of one or more transform engines that implement in hardware the transformation from object-space to eye-space, eye-space lighting and shading, and the subsequent transformation to screen-space. In this case, the CPU is left to simply generate and traverse the graphics data structures sending the object-space data to the graphics subsystem.

- **G-TXRD** Graphics subsystems of type G-TXRD are rare because of the overwhelming demand for immediate mode graphics. Moving the traversal stage from the host CPU into dedicated hardware imposes strict rules on user interaction, which is unacceptable in most environments. Because there are very few such systems, we will not discuss them further here.

Maximizing application performance on a particular type of graphics subsystem requires first an understanding of which portions of the graphics pipeline are used by an application, and second, which portions of the pipeline are implemented in dedicated graphics hardware. Keep both points in mind when authoring an application.

#### 2.1.9 Bandwidth Limitations

Another important aspect of the graphics subsystem is the physical connection or fabric connecting it, main memory, and the CPUs. Of particular relevance is the peak and sustainable bandwidth among the principal components. The physical connection can take the form of a bus or switched hub, depending on the overall architecture of the system. This connection, no matter what form it takes, has a limited bandwidth that can hinder application performance if not used effectively.

Typically, low-end graphics adapters sit directly on the 132-MB/s PCI bus where they must compete for bus bandwidth with other PCI devices. In this scenario, graphics data transferred between system memory and dedicated memory in the graphics subsystem must pass through the CPU, thereby increasing the requirements on the CPU and the risk of an application becoming CPU-bound.

Meanwhile, high-end graphics cards might use an AGP or other proprietary bus connection that offers exclusive bandwidth between system memory and graphics. Implemented using DMA, graphics data can be transferred from system memory to video memory in the graphics subsystem without increasing the

load on the CPU. This reduces the risk that an application will become CPU-bound. Currently, AGP offers an exclusive 512-MB/s or 1024-MB/s transfer path between system memory and graphics.

Another approach is the Unified Memory Architecture (UMA). In UMA machines, there is a dedicated bus that handles the flow of data between the CPU and graphics.

A comparison of the various architectures can be seen in Figure 2.9. An analysis of how different graphics hardware implementations affect overall application performance can be found in Section 4.3.4.

## 2.1.10 Larger Computing Architectures

The previous sections described the architecture of single graphics-adaptor (also know as a single head or pipe) systems. These systems are the most common types found on desktops. However, larger architectures of either multiple-pipes within a system or numbers of smaller systems clustered together provide a different set of application goals and a different set of design and usage patterns.

As computing and graphics power increases, and cost of these systems drops, systems (either single-system-image (SSI) or cluster-of-workstations (COW)) with multiple graphics pipelines (or pipes) are increasingly common. Systems of this magnitude are typically used to drive large displays such as wall or room displays, with each pipe driving a portion of that display. One common example of a system of this type is the CAVE [10]. This usage model is relatively simple to implement, as each graphics pipe contains a simple section of the overall view-frustum and the output can simply be sent to a display device. More complicated usage models will be described in which the resultant pipe outputs are not simply sent to a display device, but recombined in another pipe for scaling the graphics loads. A more general way to think of using multiple graphics pipelines to render imagery is to subdivied the entire final graphics image and farm it out to individual pipes, then recombine these images in the final display, independently of how that final display device is configured.

Why would an application use an SSI or COW system? An application should use an SSI or a COW system to display data sets much more complex than those displayed on a single pipe system. Through use of multiple pipelines, aggregate system performance is improved to a point where the problem can be interactively visualized. Though individual graphics adaptors are available on the desktop today which are more powerful in certain capacities than systems of a few years ago costing orders of magnitude more, users of systems always want to display more. Regardless of how fast individual systems perform, a combination of multiple graphics adaptors together will always be able to attack larger problems. Said differently, problem size is always increasing, and the path to attacking the largest problems today and tomorrow is to enlist multiple graphics adaptors to the same task.

Both SSI and COW systems address a similar problem, and in essence raise the system interface (PCI vs. AGP, etc.) issues to a different level. How do these systems differ, for what applications are systems like these appropriate, and how do applications utilize them effectively? The next few subsections will address these and other issues in large-system interactive graphics application utilization.

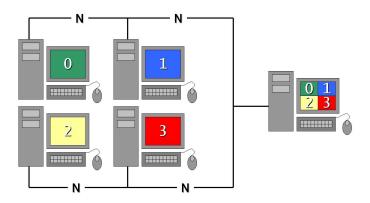

### **Single System with Multiple Pipes**

The defining features of SSI architectures are multiple graphics pipes with a single set of system resources, including memory, CPU, etc., all communicating over a high-bandwidth, low-latency interconnect. In SSI systems, all resources are available to applications through traditional programming techniques. Displays and windows are simply opened by specifying a target graphics adaptor, for example, by specifying a specific display and screen for X-windows applications. Figure 2.11 shows how a system might be configured. In this diagram, the system consists of four dedicated rendering pipelines (indicated by monitors)

Figure 2.9: Schematic of system interconnection architectures: (A) PCI, (B) AGP, and (C) UMA.

which render, transfer internally across the system's bus or hub, and then are recombined on a fifth pipe. Processes are threaded (or even forked) across multiple CPUs, and functions executed directly through standard programming language bindings. In an SSI system data is shared either implicitly, as occurs with threaded programs, or explicitly, as occurs with forked programs using shared-memory arenas. In both cases, explicit or implicit memory sharing, the data resides within a single logical memory subsystem, allowing easy and direct access to data across multiple process and threads.

Figure 2.10: Example SSI system configuration.

The key difference between systems of this type and clusters is the bandwidth and latency of interfaces among graphics pipes. In particular, in systems of this sort, sharing data from main memory to/from individual graphics pipelines is both high bandwidth and low latency.

#### **Cluster of Workstation Pipes**

The defining feature of COW systems, typically, is cost. COWs are often systems with much less integrated hardware, and more off-the-shelf components. Though systems of this sort can potentially have high-performance graphics, often they have lower cost, lower quality graphics. In COW systems, applications must be explicitly aware of the differences among individual systems, or nodes, in the cluster, as well as the individual system capabilities, and the link performance and topology of the system connections. An example of one configuration is found in Figure 2.11. Programming interfaces are explicitly parallel, or happen through an abstraction layer such as a message-passing interface. Examples of these interfaces include OpenMP [6] and MPI [4], although many others exist. One example of other techniques include distributing objects using an object layer such as CORBA [1]. Link connection and topology are key factors in constructing and using a cluster in both determining the amount of data that can be distributed to all nodes (within the application per-frame time constraints) and determining the latency involved (through number-of-hops in the topology) in transferring that data.

Figure 2.11: Example COW system configuration.

#### SSI/COW Usage Models

A variety of interesting usage patterns exist for both COW and SSI systems. In both systems, three factors are key to maximizing utilization, and all are key to ultimately achieving good results:

- Choosing an appropriate problem decomposition

- Understanding system architecture

- Understanding differences among individual systems, or nodes, within a system

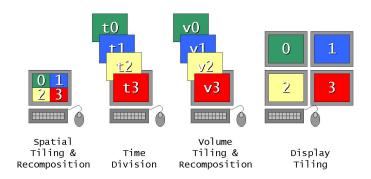

First, it's necessary to understand and choose an appropriate problem decomposition. Among the choices for problem decomposition are image-space, time-based, geometry-based, and depth-based. Each of these techniques involve understanding the desired output display configuration and configuring the set of image pipelines to produce those images.

In image-space decomposition, the configuration may consist of either a single large image subdivided into a set of smaller sub-images, or a set of abutting images, perhaps not even in the same plane, such as in a CAVE. A second decomposition is geometry-based. In this configuration, each pipe views the entire view-volume, and each pipe receives some portion of the geometry to render. One approach might simply be to send each pipe 1/number-of-pipes objects; however this approach suffers from being a bit too simple. For example, if the pipes have different capabilities (geometric or fill rates), then the goal should be to balance their workloads so that no pipe is too busy, and that no pipe is idle either. For this reason, a simple 1/number-of-pipes partitioning will likely not scale well, and the actual data needs to be examined to divide the workload equitably among pipes in a system. The images from each pipe are then recombined along with their depth values on the final pipeline.

Another decomposition, often used in simulators, is time-based. In this tiling, each subsequent frame is rendered on an additional pipe, then the results are displayed sequentially on the output device (or pipe). In time-based decompositions, pipes are arranged in a ring-buffer; each pipe, once finished, begins working on the next available frame. For non-interactive graphics applications, this technique is often used to render frames of animations, etc.

Yet another decomposition is depth-space tiling. In this decomposition, each pipe will handle the same screen-space area, but each will render a specific depth-section of the database (which itself is sorted by depth.) For example, on a three-pipe system, each pipe would create a view frustum of one-third of

the total depth. This requires that the screen-space depth data of each piece of geometry be computed. This differs from the image-space decomposition described previously in which the database is divided into eye-space sections. Each pipe renders its own piece of the entire geometry, and the rendered sets of geometry are combined into the final image.

If enough resources are available, combining these techniques can yield very interesting and scalable results. For example, an application might use a time-based decomposition, and then for each frame within that time-buffer, you can subdivide those frames spatially. Decomposition combinations such as these are extraordinarily powerful but require a significant investment in software architecture to utilize multiple-pipe systems effectively.

#### **Image-space Decomposition**

```

/* each pipe gets a section of the image-space view-volume. sort

* so only that section of data goes to each pipe. */

sort_geometry_by_pipe();

for( pipe num < num pipes; pipe num++ )</pre>

set_graphics_context_to_window_on_pipe( pipe_num );

/* OpenGL/glX: glXMakeCurrent( pipe_num ); */

render_individual_pipe_data( pipe_num );

/* OpenGL: glBegin/End */

save_image_buffer( color_buffer, pipe_num );

/* OpenGL: glReadPixels( ... GL_RGB ... ); */

}

/* ensure all pipes have finished rendering before proceeding.

* this can be optimized to allow individual pipes to proceed

* when finished. */

barrier_wait_for_all_pipes_to_finish();

set_graphics_context_to_window_on_pipe( output_pipe );

/* OpenGL/glX: glXMakeCurrent( output_pipe ); */

for( pipe_num < num_pipes; pipe_num++ )</pre>

restore_image_buffer( color_buffer, pipe_num );

/* OpenGL: glDrawPixels( ... GL_RGB ... ); */

}

/* image recomposition complete: display final image */

```

#### **Depth-based Decomposition**

```

/* each pipe gets a section of the depth-space view-volume. sort

* so only that section of data goes to each pipe. */

sort_geometry_by_pipe();

for( pipe_num < num_pipes; pipe_num++ )</pre>

set_graphics_context_to_window_on_pipe( pipe_num );

/* OpenGL/qlX: qlXMakeCurrent( pipe num ); */

render_individual_pipe_data( pipe_num );

/* OpenGL: glBegin/End */

save_image_buffer( color_buffer, pipe_num );

/* OpenGL: glReadPixels( ... GL_RGB ... ); */

save image buffer( depth buffer, pipe num );

/* OpenGL: glReadPixels( ... GL_DEPTH ... ); */

}

/* ensure all pipes have finished rendering before proceeding.

* this can be optimized to allow individual pipes to proceed

* when finished. */

barrier_wait_for_all_pipes_to_finish();

set_graphics_context_to_window_on_pipe( output_pipe );

/* OpenGL/glX: glXMakeCurrent( output_pipe ); */

for( pipe_num < num_pipes; pipe_num++ )</pre>

enable( DEPTH_TEST & STENCIL_WRITE );

restore_image_buffer( depth_buffer, pipe_num );

/* OpenGL: glDrawPixels( ... GL_DEPTH ... ); */

disable( DEPTH TEST & STENCIL WRITE );

enable( STENCIL_TEST );

restore_image_buffer( color_buffer, pipe_num );

/* OpenGL: glDrawPixels( ... GL_RGB ... ); */

/* image recomposition complete: display final image */

```

#### **Geometry-based Decomposition**

```

/* each pipe gets a fraction of the total geometric objects. each

* pipe views the entire view-volume. */

divide geometry among pipes();

for( pipe_num < num_pipes; pipe_num++ )</pre>

{

set_graphics_context_to_window_on_pipe( pipe_num );

/* OpenGL/qlX: qlXMakeCurrent( pipe num ); */

render_individual_pipe_data( pipe_num );

/* OpenGL: glBegin/End */

save_image_buffer( color_buffer, pipe_num );

/* OpenGL: glReadPixels( ... GL_RGB ... ); */

save_image_buffer( depth_buffer, pipe_num );

/* OpenGL: glReadPixels( ... GL_DEPTH ... ); */

}

/* ensure all pipes have finished rendering before proceeding.

* this can be optimized to allow individual pipes to proceed

* when finished. */

barrier_wait_for_all_pipes_to_finish();

set_graphics_context_to_window_on_pipe( output_pipe );

/* OpenGL/qlX: qlXMakeCurrent( output pipe ); */

for( pipe_num < num_pipes; pipe_num++ )</pre>

restore_image_buffer( depth_buffer, pipe_num );

/* OpenGL: glEnable( DEPTH_TEST );

* OpenGL: glDrawPixels( ... GL_DEPTH ... ); */

restore_image_buffer( color_buffer, pipe_num );

/* OpenGL: glDrawPixels( ... GL_RGB ... ); */

/* image recomposition complete: display final image */

```

#### **Time-based Decomposition**

```

/* each pipe gets the 'next' frame. the next frame is computed by

* either continuously sampling input devices, or by extrapolating

* along some smoothed previous 'n' input steps. in either case,

* each subsequent new view is rendered on another pipe, then

* back to the main pipe.

sort_geometry_by_pipe();

for( pipe num < num pipes; pipe num++ )</pre>

set_graphics_context_to_window_on_pipe( pipe_num );

/* OpenGL/glX: glXMakeCurrent( pipe_num ); */

set_view( new_view_matrix );

render_all_data();

save image buffer( color buffer, pipe num );

/* OpenGL: glReadPixels( ... GL_RGB ... ); */

set_graphics_context_to_window_on_pipe( output_pipe );

/* OpenGL/glX: glXMakeCurrent( output_pipe ); */

restore_image_buffer( color_buffer, pipe_num );

}

```

Whatever the technique chosen, the resultant images are rendered each using a different graphics pipe, and then recomposited together. Techniques for recompositing include, in the case of wall or CAVE configurations, allowing the images to simply be projected on surfaces that physically abut each other, thereby creating the illusion of a seamless image. The second, more challenging technique, involves rendering images on a number of pipes, then capturing those pixels (and potentially depth information), and sending them back across to the final graphics pipe where they are recomposited together, then sent to the display device. Examples of all these techniques are shown in Figure 2.12.

The above description brings us to the second and third key points to effectively utilizing a multiple-pipe system. The second key factor is to understand the system architecture. In some architectures, bandwidth may not be available to pass back image sections to a final pipe for recompositing. Or, potentially, if bandwidth is available, the latencies involved may be too long for a copy to occur per-frame. For example, in a COW, latencies may be on the order of several milliseconds, but in an SSI system, latencies may be on the order of several microseconds. In clusters, at this point in time, a good strategy is to avoid these latencies whenever possible by transmitting synchronous data across the network fabric as infrequently as possible. This also implies that, for COWs, depth-space compositing can be difficult, again due to the latencies, especially in interactive applications. Specifically, a good technique in COWs is to project the resultant displays to recomposite the image. Similarly, in an SSI system, where latencies are lower, it's much more feasible to transmit portions of the resultant image to a single pipe for recompositing.

Figure 2.12: Example tiling techniques for scaling graphics performance.

The last key factor in using a multiple-pipe architecture is to understand the differences among individual systems, or nodes, within a system. When doing depth-space compositing, or large image reconstruction, doing this final step on a system with additional resources makes obvious sense, as the pixel demands on this system will be larger. In a more general sense, balancing the load among systems in either a COW or an SSI system is essential to maximizing the performance of the overall system. Both geometric and fill requirements should be balanced for each individual node and pipe within a system so that each pipe is kept busy, but only for as long as the time constraints on interactivity allow.

# 2.2 Graphics Hardware Specifications

### 2.2.1 Graphics Performance Overview

Graphics hardware vendors typically list several gross measurements of system performance when releasing new graphics hardware. Many of these measurements are benchmark data showing how hardware performs with a real set of data. Often these figures are not representative of how an application performs. Vendors typically list even more coarse measurements for their graphics hardware such as fill rate and polygon rate. Most, if not all, of these numbers should be viewed with a fair degree of skepticism and then independently verified.

# 2.2.2 Graphics Performance Terms

Fill rate is a measure of the speed at which primitives are converted to *fragments* and drawn into the framebuffer. Fragments are pixels in the framebuffer with color, alpha, depth and other data, not just the raw color data that appears in an image. Fill rates are reported as the number of pixels able to be drawn per second. This number is virtually meaningless without additional information about the type of pixels (and more correctly, type of fragments) that are involved in the measurement. Read literature carefully for additional information about the tests including what bit-depths each of the fragments used (32-bit RGBA, 8-bit RGB, etc.), whether or not the fragments were textured, what type of texture interpolation was used, and so on.

Fill rate consists of more than simply the number of fragments drawn to the framebuffer and transferred to the screen. While drawing geometry to the framebuffer, fragments can be filled multiple times. For

example, if a polygon at some far distance in the framebuffer is first drawn and then another is drawn in front of it, the second polygon will be drawn completely, overwriting some of the farther back polygons. Pixels in which the two polygons intersect will have been written to, or filled, twice. The phenomenon of writing the same framebuffer fragments multiple times yields a measurement know as the *depth complexity* of a scene. Depth complexity is an average measurement of how many times a single image-pixel has been filled prior to display. Applications with high depth-complexity are often fill-limited. Fill rate is often a bottleneck for application domains such as flight simulation.

*Polygon rate* is a measure of the speed at which polygons can be processed by the graphics pipeline. Polygon rates are reported as the number of triangles able to be drawn per second. Polygon rates, like fill rates, are almost meaningless without additional supporting information. Check hardware information carefully for specifics about whether or not these triangles were lit or unlit, textured or untextured, the pixel size of the triangles, etc. Polygon rates are often bottlenecks in application domains such as CAD and manufacturing simulation.