# An Explanation of the Advantages Afforded by QED RM5200 and MIPS RI2000 CPUs in O2.

Authored by: Ian Williams

The Silicon Graphics 02 was a catalyst to broad acceptance and adoption of integrated graphics and digital media in the low-end UNIX desktop market. Through its highly innovative architecture, it revolutionized the way graphics features such as texture mapping and digital media technologies, such as video capture and playback, could be delivered in an affordable system.

The O2 architecture allows these diverse types of data to be created, manipulated and integrated readily, allowing users to work much closer to their mental vision of their products. Those products can be as diverse as an oil drilling platform or an animated cartoon character. Indeed, within the UNIX market many O2 capabilities remain unsurpassed, even when compared to significantly more expensive systems.

The upgrade of the O2's CPUs from the MIPS R10000 to the MIPS R12000 and the MIPS R5000 to the QED RM5200 allows the platform to deliver significant performance increases in both computational and graphics-related usage. This whitepaper describes the benefits the new CPUs bring to both low-level graphics and real world application performance in markets where O2 adds real value. It also demonstrates O2's strengths relative to competitive systems in these markets. Compared to many O2s used by existing customers, the performance of systems incorporating the new CPUs can provide end user productivity gains significantly over 100%.

### White Paper

Table of contents

### 1. Introduction - Current State of Play

This section briefly presents a real-world example which succinctly characterizes the clear and unique benefits afforded by 02 as well as presents the distribution of 02 units/revenue across market segments.

### The End User Benefits and Competitive Advantages Afforded by O2's Architecture

This section describes some elements of 02's architecture in detail and its strengths relative to competitive systems and architectures in relation to the key graphics digital-media technologies of:

- 2.1. Texture Mapping

- 2.2. Image Processing

- 2.3. Video processing, compositing and virtual sets.

The computational strengths of O2's CPUs are discussed in the section on:

2.4. Computation Performance and Overall System Throughput

Which also highlights the positioning of MIPS R5000 relative to MIPS R10000 based systems as well as relative to competitive products.

### Comparison of New and Existing 02 CPUs.

The section is divided into three parts and describes in technical detail the key differences between the existing and the new CPUs incorporated into O2 as well as the two CPU families.

- 3.1. Description and Comparison of MIPS R5000 and QED RM5200

- 3.2. Description and Comparison of MIPS R10000 and MIPS R12000

- Summary of Differences Between QED RM5200 and MIPS RI2000

### 4. An Illustration of the Synergy between 02 CPUs and Architecture for Graphics.

This section demonstrates how the combination of CPU architectural changes in both the QED RM5200 and the MIPS RI2000 combined with the 02 architecture yield performance increases that are higher than clock — an example of the true definition of the word synergy.

- 4.1. Triangle fill-rate

- 4.2. Textured triangle fill-rate

- 4.3. Texture up-load

### 5. Translation of Improvements Afforded Through the New CPUs Into End User Benefits

This section builds upon the examples presented in the last section and shows how the new CPUs yield significant improvements in end user performance, which in turn translates to improvements in productivity.

### 6. Conclusion - Resuming play

This section concludes by summarizing the advantages afforded 02 by both the QED RM5200 and MIPS RI2000 and positions the 02 against some of the current competitive systems, highlighting both strengths and weaknesses of all systems.

Introduction - Current State of Play

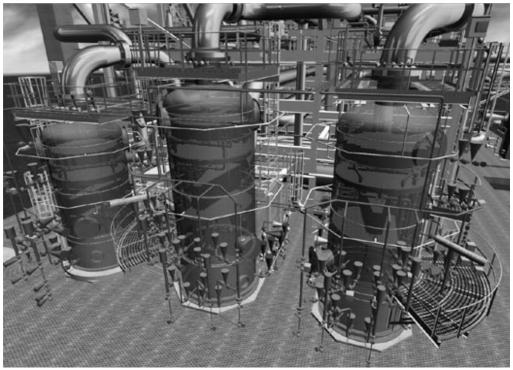

Figure I, "The "Ist and IO" line makes its mark" [1], [2] and Appendix I.

Most readers will at least recognize the image in Figure I, even if they aren't avid American football fans. At first glance though, it would be easy to miss its relevance to this paper and what it really represents. On closer study, those readers more familiar with American football may speculate the state of play or even possibly the outcome of the game. Most non-football fans, probably wouldn't pay much attention to the yellow line marking the 1st down line. Although a simple element of the picture, the yellow line represents a significant step forward in technology made possible by the architecture and integrated features of the Silicon Graphics O2 system. Its oversight by many readers should, therefore, be taken more as a compliment than an insult.

A few years ago it wasn't practical to contemplate using a simple visual effect such as superimposing a yellow line onto live video footage. Now though it is a fairly familiar sight, especially to American foot-

ball fans. The Silicon Graphics 02 system made this possible by integrating graphics and digital media technology in a seamless and efficient way at a low cost. It affords many unique advantages compared with competitive systems in its class and offers features that were previously only available on dedicated one-off systems that were significantly more expensive, in some cases even up to orders of magnitude so. As a result of the 02 system, its realistic to contemplate using these features on a day-to-day basis, which clearly demonstrates significant real world benefits to end-users.

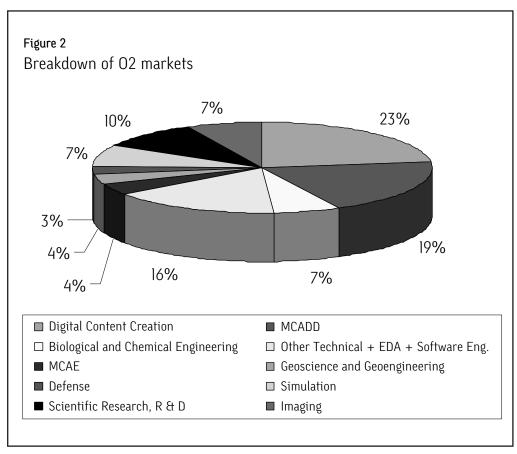

Because the example presented relates to the broadcast industry it would be easy to think that the benefits afforded by O2 are restricted to this and similar markets. The distribution of O2 units across different market segments, shown in Figure 2, clearly demonstrates O2's widespread appeal across all industry segments.

Figure 2, Breakdown O2 market segments based on units/revenue.

Clearly the greatest number of O2 systems are sold into the digital content and creation [DCC] market which includes the application presented above. This is because in this market both O2's architecture and features make it an obvious fit. Clearly though the Mechanical Computer Aided Design and Development [MCADD] market is a close second. In this case features such as client scalability coupled with a balance between visualization and compute capability make O2 an extremely attractive low cost proposition in the UNIX market place. Likewise, these features also make O2 attractive to the Scientific Research and R&D, as well as Simulation, Imaging and Biological and Medical engineering markets.

Given 02's clear appeal across all these markets, what aspects of its design contribute to its popularity? The next section aims to address this question by describing in detail many of the unique features of 02's architecture, highlighting differences to competitive systems and architectures and showing how these differences translate into end user benefits.

#### x 144 SDRAM SIMM MIPS R5000 and QED x 144 SDRAM SIMM RM5200 based systems Memory x 144 SDRAM SIMM x 144 SDRAM SIMM Secondary Cache R5000 CPU Memory and Rendering Engine(MRE) Sys AD Bus MUX/DFMUX Processor Module Imaging nd Compressio Engine (ICE) CPII VDAC L2 Cache Adapter ICF 533MR/s MIPS R10000 and MIPS R12000 based systems Serial Porti/ Memory I0E Secondary Cache RTC ROM Line Out 2 Sys AD Bus External F20WSCSI Rendering Engine[MRE] FROWSCSI System Disk Imaging nd Compressio Engine (ICE) PC164 Slot Data Disk Optional, depending on configuration CPU Interface ASIC

### The End User Benefits and Competitive Advantages Afforded by O2's Architecture

Figure 3 Diagram of O2 system Architecture.

Figure 3 shows a detailed block diagram of 02's architecture. As can be seen from the diagram it comprises of five key units: main memory; the Processor Module which includes secondary cache and the Image Compression Engine; the Memory Rendering Engine, and both the Display and I/O Engines.

Many readers will be familiar with the function and operation of each of these units and, to a high-level at least, they should be fairly self-explanatory. Some of the sub-sections below, such as when discussing the technical strengths of O2's architecture in more detail, as well as later sections in the paper, assume more than a very high-level appreciation of O2's architecture. In such sections sufficient background informa-

tion is given to appreciate the points being discussed, however, inevitably some details probably don't receive as much attention as perhaps they should. To this end readers are invited to refer to[3] for further details and information on 02's architecture and components.

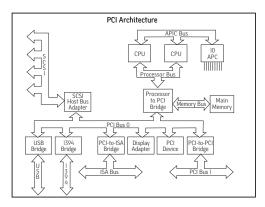

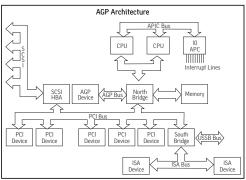

R10000 and R12000 systems only

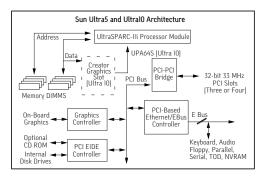

For comparison purposes, figures 4a and b show generic low-cost architectures based on PCI and PCI combined AGP respectively. Figure 4c shows the architecture of Sun's Ultra5 and Ultra10 systems. For more information and details on both PCI and AGP architectures and capabilities, see [4] and [5]. For more information on Sun's Ultra 5 and Ultra10 system architectures see [6], and see [7] for further information on Sun's UPA graphics connection.

Figure 4a, 4b and 4c. Diagrams of: Generic PCI bus based architecture; Generic architecture using both PCI and AGP busses, and Sun Ultra5 and Ultra10 architecture.

Clearly when comparing 02's architecture to typical competitive systems it is easy to see that it represents a major departure from typical solutions and hence it may be tempting to think of it as unnecessarily complex. Apart from perhaps being somewhat short sighted, this misses several key points. To explain the motivating factors behind it, consider an analogy of traveling by car or airplane. A journey by car at first sight may appear significantly less expensive than a journey by aircraft, as well as offering much greater convenience etc. These advantages, however, reduce dramatically when travelling more than a few hundred miles. Taking into account the true cost of ownership, as well as cost implications arising from time spent traveling, it is easy to see why the car soon becomes significantly less attractive when covering more

ground. Also, a major factor in the apparent convenience afforded by a car arises from the ability to travel between two destinations via several alternative routes, as occurs within suburbs and cities. Over larger distances these routes typically amalgamate into a small number of key routes, between states or countries say, and hence offer no advantage over the defined routes used by aircraft.

As the example clearly illustrates, when travelling between any two destinations most people choose between a car or an airplane depending on which is more appropriate for the length of the journey as well as other factors. The reason for O2's departure from more traditional architectures was, therefore, to produce a system that allowed users to translate and manipulate their mental vision of an idea in an easy, effective and efficient way. To do this requires being able to manipulate and combine diverse types of digital data, such as 3D geometry, images, video or audio, in a seemless and integrated fashion. In the same way, people in the real world aren't restricted to always using a car or an airplane for all journeys regardless of length. O2's architecture allows the most appropriate data to be used to describe some aspect of an idea or product and since the capability is offered at a low-cost, it exemplifies why O2's architecture can be considered ground breaking and also represents a major step forward in the computing industry.

At first sight it may appear as though O2's architecture would result in a more expensive system compared to utilizing CPU performance to perform many activities. It should be appreciated, however, that once a design is committed to silicon, production costs are very low. It's interesting to note that the cost of additional CPUs in competitive machines is significant when compared with the price of an O2 system. Of course, due to the unique architecture of O2 doesn't reguire additional CPUs for many sophisticated tasks. The benefit of 02's architecture to the end user is clearly that it not only delivers both advanced and sophisticated digital media capabilities at a very low cost, but also doesn't incur significant additional costs, such as multiple CPUs, to be able to fulfill expectations and deliver acceptable performance.

In many situations it is appropriate to use system resources for a variety of uses, for example using main memory instead of dedicated texture or video memory. Through the design of O2 this incurs no performance penalty and affords considerable flexibility to meet widely varying needs of applications across all market places. It also reinforces the strengths of O2's design in delivering sophisticated features and functionality as well as being able to cope with many conflicting requirements for low system cost. After all, with the exception of Silicon Graphics' 320 and 540 platforms, no other technical workstation currently sold under \$8K dollars provides up to 1 Mb of texture memory and offer many sophisticated digital media features, such as real-time uncompressed video capture/ playback and real time 3D video textures.

High-level intent and good design, however, do not directly equate to end user benefits. To demonstrate the benefits afforded to the end user by 02, its necessary to consider specific examples of digital media technologies and how they relate to typical user activities. In this way the strengths and unique features of 02's architecture can be highlighted in comparison to alternative system architectures and the end user benefits demonstrated. To this end, the remaining part of this section concentrates on three graphics and digital media technologies, Texture-mapping, video processing and imaging, showing how they relate to typical user activities and the benefits afforded through 02's architecture.

### Texturing Mapping

Most readers are probably very familiar with the concept of texture mapping. Indeed, in the Digital Content Creation and Architectural Engineering market places it is an accepted feature in widespread use. A good description of the many incarnations of texture mapping is presented in [26], however, perhaps the most widespread use is where it appears as if a two dimensional image is applied to a 3D object within a model or scene. This dramatically increases the realism of computer, or digital representation. Figure 5 shows an example taken from an application called Review Reality produced by CADCENTRE (UK). Texture mapping can also be used to create better lighting effects on models and components, such as would be needed to correctly represent the effect seen when shining a particular spot light on an object.

Figure 5, An example of texture mapping taken from the CADCENTRE Review Reality program.

To assist a user's creativity and be of real benefit, it is important to be able to interact with such a model or scene so that the full implications of individual components can be appreciated. When using texture mapping, doing this requires the image data to be referenced each time the scene is drawn. If manipulation is to be interactive, this equates to many times a second. To illustrate the system requirements this can create, consider that a true color image 1280x1024 pixels in size corresponds to 3.9 MB of data. Even though 1280x1024 pixels may be considered large

relative to some images, it does correspond to the display resolution of most workstations as well as the current resolution of higher performance digital cameras. Likewise, drawing a model or scene 60 times a second may be considered fairly optimistic, however, it is considered a good threshold above which the eye is unable to discern discrete movement and hence most good computer displays refresh at this rate and above.

Transferring the image between main memory and the graphics subsystem at these rates requires a bandwidth of 236 MB/s [3.9x60]. This figure also represents the sustained, not the peak requirement, and also does not take into consideration the transfer of additional data necessary for a scene such as 3D geometry or even additional textures. To make a system acceptably interactive when using texture mapping, clearly a significant amount of data needs to be moved. From a system architecture viewpoint two approaches are typically adopted to solve this problem.

The first approach is to use dedicated texture memory on the graphics board where textures are downloaded and stored. This has the advantage that the data can be contained within the graphics subsystem and hence does not invoke the transfer from memory during each frame. Indeed this is the way adopted by most traditional computer architectures. The disadvantage with this approach is that texture memory local to the graphics subsystem is typically expensive because it is high speed. When texture mapping is not required, therefore, this additional cost is not being utilized. There is also only a finite amount of dedicated texture memory is available and hence when using a large number of textures its likely that some will not fit in local texture memory and have to reside in main memory instead. Clearly this pushes up the system bandwidth requirements. These can in turn create more complexity in application programs since additional functionality may be desired or in fact required to efficiently cache textures on the graphics board.

An alternative approach, and one that is also being promoted by Intel through its AGP bus specification, is to utilize main memory to store textures. Since there is typically a significantly greater amount of main memory than there is dedicated texture memory, this approach potentially offers significant cost savings. Simply by adding more main memory, the capacity to store textures can be increased and typically main system memory is noticeably less expensive than dedicated texture memory. Also when texture mapping is not required main memory can be used for other purposes. Unfortunately though, as the above calculation clearly demonstrates, this approach relies heavily on a significant bandwidth between main memory and the graphics subsystem. The AGP bus is dedicated purely to graphics and hence goes some way to address this particular problem. It should be noted though, that the AGP specification does not actually preclude it being used for other devices as well as graphics.

Given that AGP Ix, 2x and 4x have peak theoretical bandwidths of 266 MB/s, 533 MB/s and 1066 MB/s, respectively, it is easy to see why most high-perfor-

mance graphics cards implemented using AGP typically contain dedicated local texture memory. Indeed, AGP bandwidth figures quoted here are actually peak and hence even though texture transfers allow rates close to peak to be achieved, the actual achievable sustained transfer rates will be slightly less than these figures show. When transferring other graphics data such as vertices and normals the transfers are often more bursty in nature and in such cases sustained AGP transfer rates are significantly lower than those given above. So although AGP aims to address the problem of designing a system to be low cost while still be able to perform sophisticated features such as texture mapping, it still has noticeable limitations.

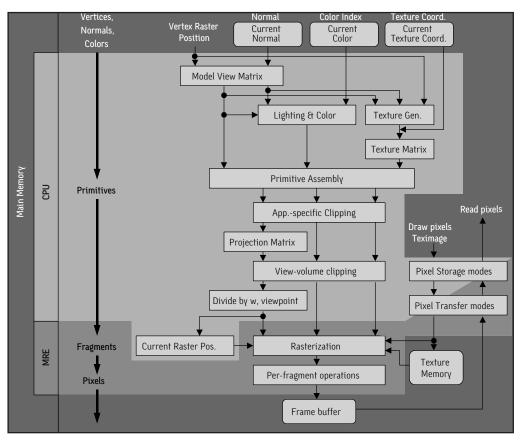

The architecture of the Silicon Graphics O2 system addresses the problem by combining the best features of the above two approaches. Combining the function of the memory controller and rendering engine into a Memory Rendering Engine (MRE), see Figure 3, effectively moves the graphics card significantly closer to both memory and the CPU. Because of this the bandwidth between the MRE and memory can be significantly increased to its current rate of 2.1 GB/s. Clearly this is also a dedicated connection. The bandwidth between the MRE and CPU is less than this, however, by appropriate design of the graphics functionality in the MRE the need for the CPU to process data during graphics is reduced and hence the bandwidth of this bus does not become a limitation. Clearly for texture mapping, the 2.1 GB/s connection between memory and the MRE is the link over which textures will be transferred during graphics. When compared with the 960 MB/s [@120 MHz] UPA64S bus in the Sun Ultra5 and Ultra10 as well as the 266 MB/s, 533 MB/s and 1066 MB/s offered by AGP Ix, 2x and 4x bus, the O2 bandwidth is clearly significantly larger.

This larger bandwidth doesn't directly equate to overall graphics performance, however, since a large element of overall graphics will relate to geometry processing capability as well as the effects of other activities that occur during dynamic graphics within an application. To this end many of 02's competitive systems, such as the Ultra5 and Ultra10, have significantly more geometry processing capability and hence in many situations may appear faster. Focusing on pure texture mapping activity, however, shows 02's strengths. Unfortunately in published product literature, e.g. [7] and [8], as well as the industry standard graphics benchmark results, [9], there is there is little data relating to Sun's Elite3D graphics texture mapping performance.

### Image Processing

Image processing is a large requirement in both the DCC and medical imaging markets. Many applications such as Adobe Photoshop and Premiere are frequently used to perform many sophisticated imaging functions. At a low level, however, all these applications rely heavily on the ability of a system to move data to and from the CPU and memory with low latencies.

O2's architecture is ideally suited to these types of operations due to the close, high-bandwidth link between main memory and the MRE as well as the Image Compression Engine [ICE]. The ICE offloads the CPU when performing imaging operations, which significantly improves performance. From a user perspective this doesn't equate to an increase in productivity unless such performance can be utilized transparently. To that end the ICE is designed to accelerate the industry standard OpenGL imaging extensions and hence is able to offer such functionality to the user in a transparent way.

Unfortunately, there aren't many industry standard benchmarks related to these activities and hence it is difficult to show O2's strengths through benchmark results. By way of demonstration, however, the "Roam" program included in the standard demo suite on most Silicon Graphics machines provides a very good example of the power and facilities available on O2. The program allows a IKxIK image of the San Francisco Piers generated from a Satellite photograph to be rotated, translated and zoomed in perfect real time. Through its architecture, 02 is ideally suited to more sophisticated image processing activities. The Distort demo is also a good example of the power of O2's architecture, remembering that the system lies within the low-cost UNIX market space. The Distort demo presents a photograph that is texture mapped onto a polygonal surface. The surface can be distorted by either introducing ripples by clicking the cursor or by dragging a point upwards in 3D space. After distorting the image in these ways as it returns to its default flat state the photograph realistically depicts the effect that would be seen. Figure 6a and 6b show a screen shot from both Roam and Distort, respectively

Figure 6a and 6b, Images from the Roam and Distort demos respectively.

### Video Processing, Compositing and Virtual Sets

Low cost video processing is an area that is increasing in popularity within the DCC market space. Indeed the example of the virtual 1st down line presented at the start of this paper is a very good example of compositing. This is by no means the only example of compositing; most readers are probably familiar with seeing the picture behind the news announcer changing to represent the current story. This again is an example of compositing. Many readers may be familiar with the concept of virtual sets, where an actor or anouncer are recorded against a blue or green screen and then the resulting live action is combined with a computer generated scene taking into account the movement of the person within the overall scene. All these examples show that the use of both compositing and virtual sets are gaining widespread use and the results are becoming increasingly more commonplace.

Texture mapping and Image processing, video processing, compositing and virtual sets rely on low-level system features that represent key strengths of O2's architecture. For example the close coupling of the Display Engine (DE), MRE and I/O Engine (IOE) allow real time uncompressed video to be saved to disk. The features built into the IOE provide native support for non-square pixel format and square pixel format conversion in real time allowing in-coming video signals to be displayed with the correct aspect ratios. The IOE also provides support for real time color space conversion, allowing incoming video signals to be processed and stored in 4:2:2YcrCb format and then converted in real time to 8-bit per component RGB a format for use as textures. When this capability is combined with 3D graphics this presents a very powerful set of features, which are unrivalled by Sun or any of the other competitors at 02's price point. These features are integrated into the standard OpenGL imaging extensions thereby allowing applications to take maximum advantage with minimal effort. Adobe Premier's transition and 3D special effects plug-ins are an example of one such application.

As shown earlier, O2 was deliberately designed so that the video processing components were de-coupled from the IOE and MRE functions. This allows flexibility in configuration to meet customer needs - not everyone will want video in or out capability. What it does mean though, is that the sophisticated video processing capabilities are available to everyone. To that end if video data originates from disk or network, such as an MPEG stream, then any O2 is capable of using it as a source for texture maps etc. This is a distinct advantage over competitive systems.

Integrating image and video processing functions into the core components of O2's architecture and closely coupling these components together offers several benefits which translate to cost savings compared with traditional ways to incorporate such features. For example because the IOE and ICE are closely coupled to main memory it removes the need for local buffers in the video data paths, with no impact on features of performance. This directly translates to end user benefits on one level of pure cost savings and on another by facilitating such advanced features as being able to use video data for textures. More traditional approaches to incorporating such facilities include incorporating them onto a PCI card. As highlighted by the texture-mapping example above, PCI bandwidth makes providing features such as live video textures very difficult

Sun is promoting media extensions to their instruction set [10], [11], [12] which they claim when combined with their Ultra Port Architecture [UPA] [13] provide a powerful system with the necessary bandwidths to perform digital media facilities. While it is true that Sun's UPA offers respectable system interconnect bandwidths, 1.92 GB/s between CPU and UPA and 960 MB/s between UPA and graphics, the UPA architecture does not offer the same advantages as 02. Indeed using the CPU for digital media processing may yield several major disadvantages from an architectural perspective.

Using the CPU to perform digital media functions such as video processing is likely to result in it becoming a noticeable bottleneck. It will need to perform other tasks such as executing the operating system as well as even elements of graphics calculations depending on the nature of the hardware graphics being used. For video processing, very low latencies and guaranteed processing resource are pre-requisites. Because the IOE and ICE in O2 are specifically designed to perform such functions, they can easily accommodate both these pre-requisites without also being required to do unrelated activities like running the operating system. Performing the same functions as the IOE and ICE on the CPU through media extensions makes accommodating both these pre-requisites considerably more difficult due to the time-slicing nature of how a CPU operates. Additional CPUs may potentially appear to offer a solution, however, apart from increasing cost, it should also be noted that with the UPA architecture, all CPUs will share the 1.92 GB/s to the UPA switch. This may lead to contention since processing video data on the CPU will typically result in several read and write operations. All three alternatives have to fight for the bandwidth across the connection between CPUs and UPA switch. Even though the bandwidth between the IOE and MRE is only 533 MB/s, the IOE performs all necessary video conversion etc. as they data arrives and hence the bandwidth is more than adequate to transmit processed data through the MRE and into memory. Likewise, although it may appear that the bandwidth between the CPU and MRE could be a limitation compared with 1.92 GB/s with Sun's UPA architecture, for applications like video processing and texturing the MRE operates on data directly in memory. The bandwidth of this connection is 2.1 GB/s and is clearly significantly higher than that of the UPA. As a result performing advanced digital media features such as video texturing is guite possible with every 02 system.

This section has tried to provide a sample of the benefits afforded to the video processing end user by O2's architecture and features. Inevitably though because the list of such benefits is very long there isn't enough space to cover anywhere near all of them. For a more complete list, as well as further details, the reader is invited to refer to [14]. A very good demonstration of the synergy these feature can yield when applied to video processing is the "VideoDistort" and the "polyVideo" demos which are included on the standard Silicon Graphics 02 demo suite. The VideoDistort demo shows how live video can be used as a texture map onto a 3D surface which can be distorted. Likewise the polyVideo demo shows the types of 3D effects that can easily be created for transitions between video streams by applying video data as textures to morphing 3D surfaces. Figure 7a and 7b show images from the VideoDistort and the polyVideo demos respectively.

Figure 7a and 7b, Images from the VideoDistort and polyVideo demos respectively.

## Computation Performance and Overall System Throughput

The three previous sections demonstrated the strengths of O2's architecture and features by relating some key graphics and digital media technologies to real world examples. This section discusses the wider issue of where 02 benefits end user productivity through computation and system throughput. This is an important aspect of system performance in all market segments, especially when application software architectures are evolving to utilize plug-ins. These plug-ins are often developed by software vendors independent of the application vendor producing the software in which the module plugs in. In some cases such as Adobe Premier's transition and 3D special effects plug-ins mentioned above, these plug-ins take advantage of the sophisticated digital media features of O2's architecture, however, most typically rely heavily on the CPU. To this end incorporating specialized functionality into the MRE, IOE, ICE and DE in O2's architecture not only delivers better overall system performance for specialized features, but also noticeably reduces the load on the CPU. This allows it to dedicate more time to perform additional computations that maybe required.

The computational requirements of all users typically won't be the same and likewise all users typically won't have the same constraints on factors such as overall system cost etc. To accommodate these varying needs, 02 incorporates two CPU families: The first family is based on the MIPS R5000 and now the QED RM5200 CPUs, and the second is based on the MIPS R10000, and now the MIPS R12000 CPUs. Both families offer specific characteristics and features and some of these will be covered in more detail in the next section comparing the new and existing CPUs in both families. To understand the benefits afforded through O2's architecture though, it is useful to have an appreciation of the benefits both CPU families bring and the relative positioning. The rest of this section presents such an appreciation as well as positioning O2 against some competitive systems.

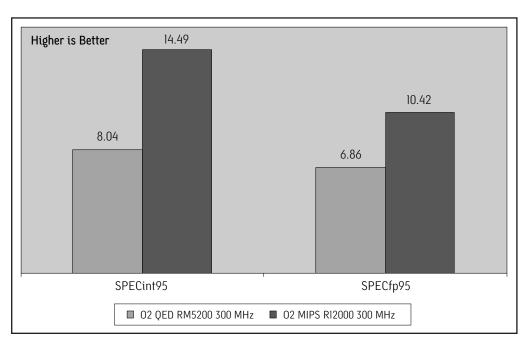

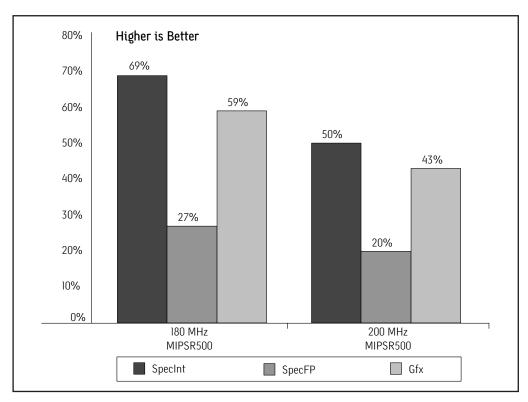

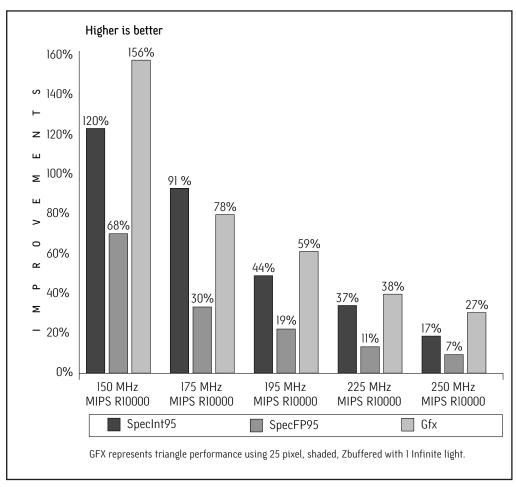

The industry standard SPECint95 and SPECfp95 suite of tests represent a cross-section of applications, exhibiting both integer and floating point behavior respectively, and are useful to characterize CPU performance. Figure 8 shows the relative performance of the QED RM5200 300 MHz and MIPS R12000 300 MHz based 02 systems.

Figure 8 Relative SPECint95 and SPECfp95 performance of QED RM5200 300 MHz and MIPS RI2000 300 MHz based O2 systems.

Clearly the results show that compared with QED RM5200, MIPS RI2000 exhibits stronger integer and floating point performance. When workloads involve applications demanding significant amounts of computation, MIPS RI2000 would therefore be the typically CPU of choice. This doesn't, however, convey the whole story regarding the relative performance of QED RM5200 and MIPS RI2000 based O2 systems.

Like MIPS R5000, the QED RM5200 microprocessor was designed to be a low cost 32-bit CPU, taking advantage of the MIPS IV instruction set. The MIPS IV instruction set includes many instructions such as multiply-add. As will be covered in more detail in the section entitled An Illustration of the Synergy between O2's CPU and architecture for graphics, the

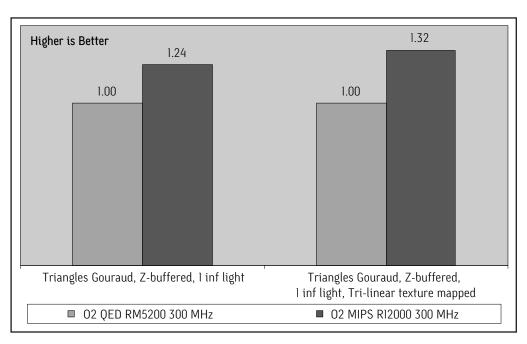

MRE utilizes the CPU for appropriate tasks in the OpenGL graphics pipeline. Instructions such as the multiply-add instruction are particularly suited to this type of calculation since they save a significant number of CPU cycles compared with performing such operations individually. The graphics libraries supplied as standard on QED RM5200 based 02 systems, and previously MIPS R5000 systems, have been optimized to take advantage of such MIPS IV instructions with noticeable improvements in graphics performance. To illustrate this point, Figures 9 shows the relative graphics performance of QED RM5200 and MIPS R12000 based 02 systems.

Figure 9 Ratio of graphics primitive performance of QED RM5200 300 MHz and MIPS RI2000 300 MHz based 02 systems.

Clearly, QED RM5200 based 02 systems deliver good graphics performance relative with MIPS RI2000 based 02 systems and provide a strong low-cost entry point to the sophisticated digital media features afforded by 02's architecture. Indeed many frequently performed tasks in DCC and AEC applications typically yield integer dominated behavior at a low-level, and hence the power of QED RM5200 based 02 systems more than satisfies many users needs. This strength combined with the very strong client-server scalability of the Irix operating system, presents a very attractive solution to many customers. Where customers require stronger computational performance, such as when applications typically yield more floating-point oriented behavior, MIPS RI2000 based 02 systems are typically preferred.

Since 1993 the MIPS microprocessors based Silicon Graphics systems have led most of the industry by being 64-bit addressable. Likewise, in 1996 Silicon Graphics' Irix operating system was ahead of most of the industry in providing a full 64-bit operating system across its entire product line and is the same operating system that runs on both QED RM5200 and MIPS R12000 based 02 systems.

This scalability of the operating system across the entire product line actually makes O2 systems very attractive to many customers as a development machine. Although this feature doesn't typically take advantage of any of the digital media capabilities of an O2 system, it does offer a very good platform on which to develop applications that would typically to run on Silicon Graphics' very high end graphics and supercomputer systems.

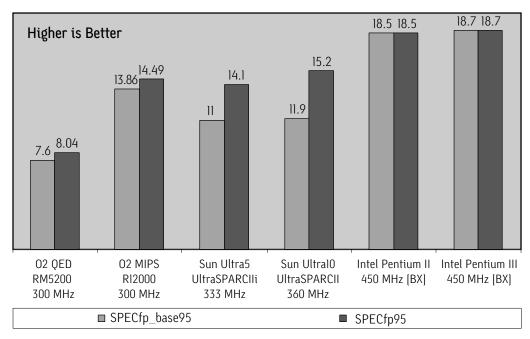

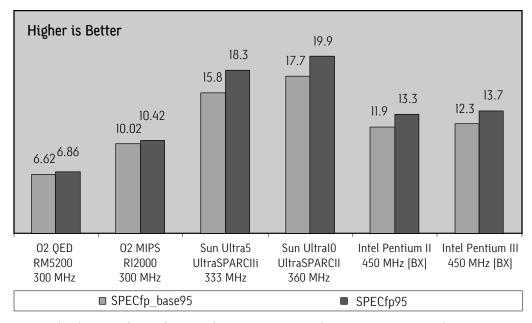

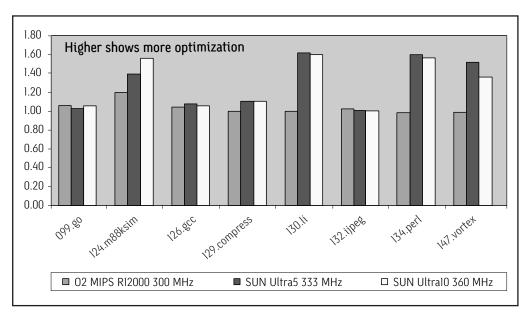

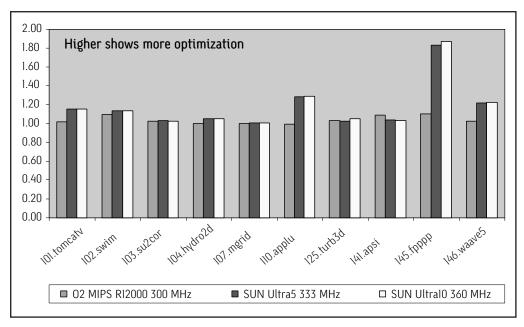

Given the positioning of QED RM5200 and MIPS RI2000 based 02 systems, how do they compare with competitive systems? Figures I0a and I0b show the performance of both QED RM5200 300 MHz and MIPS RI2000 300 MHz based systems relative to competitive systems [15], [16].

Figure 10a Relative SPECint95 performance of competitive systems and QED RM5200 300 MHz and MIPS R12000 300 MHz based O2 systems.

Figure 10b Relative SPECfp95 performance of competitive systems and QED RM5200 300 MHz and MIPS R12000 300 MHz based O2 systems.

Based on the SPEC results shown in Figures 10a and 10b, it would tempting to think that 02 offers few advantages over the Sun Ultra5 and Ultra10 systems and Intel based systems. While it is true that the SUN as well as Intel based systems demonstrate performance advantages in SPECint95 and SPECfp95 results, it is not true that this will be representative of application performance. To illustrate how large the difference

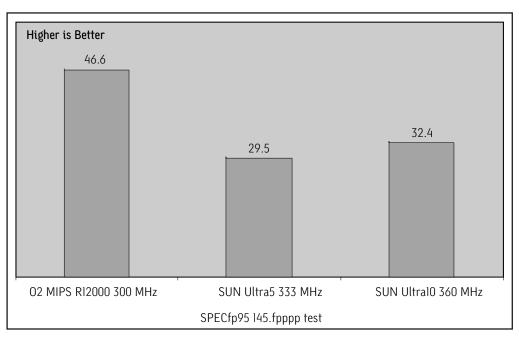

between SPEC and application performance can be, Figure II shows the performance of a MIPS R10000 based 02 system compared with Sun Ultra5 and Ultra10 systems on the 145.fpppp test which is part of the SPECfp95 suite. These results clearly show 02 to have a very distinct advantage even compared with the comparable Sun systems.

Figure II, Performance of MIPS R12000 300 MHz based O2 system compared with Sun Ultra5 and Ultra10 systems for SPECfp95 145.fpppp test.

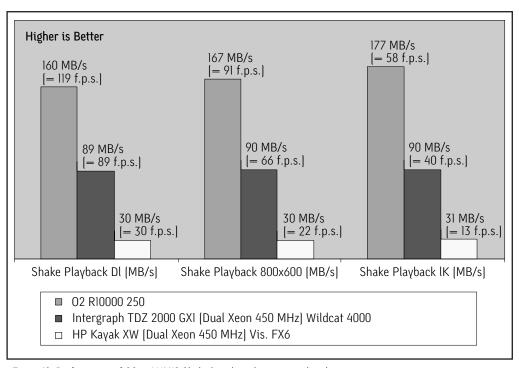

Figure 12, Performance of 02 in LUMIS Shake benchmarks compared with competitive systems.

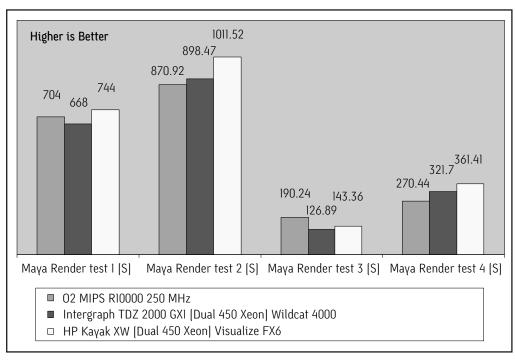

To further illustrate the same point, Figures 13 and 14 show the performance of a MIPS R10000 based 02 system compared with competitive Intel CPU based systems measured using the Shake and Maya rendering

benchmarks run by LUMIS inc., [17] and [18]. Again a different result is seen as would have been expected from the SPEC results alone and they clearly show how 02 performs well on many real applications.

Figure 13, Performance of O2 in LUMIS Maya Render benchmarks compared with competitive systems.

The LUMIS Shake benchmark measures a systems ability to replay movie data from disk which is an activity frequently performed in digital editing markets and one particularly suited to the strengths of 02's architecture. Clearly on such activities 02 demonstrates a very significant advantage above high-end competitive systems. Likewise for the more computationally dominated Maya rendering benchmark, the MIPS R10000 250 MHz based 02 system shows comparable performance with the same competitive systems and an 18% advantage over its nearest rival which uses dual Pentium II 450 MHz Xeon processors.

Clearly this is not intuitive from the slight performance disadvantage the same MIPS R10000 based O2 system shows in SPECint95 and SPECfp95 relative to a single Pentium II 450 MHz Xeon processor. Typically real world applications highlight the hidden strengths of the O2 system. Combined with the features afforded through its architecture that are unsurpassed by competitive systems, O2 presents a very compelling solution.

### Comparison of New and Existing 02 CPUs.

This section presents detailed technical information on the two new CPUs available in O2 systems. The first subsection describes the MIPS R5000 and the QED RM5200 microprocessors, while the second subsection describes the MIPS R10000 and MIPS R12000 microprocessors. The third subsection covers some of the motivations for the architectural differences between the QED RM5200 and the MIPS R12000 systems.

The section assumes some knowledge of microprocessor architecture and design and unfortunately there

isn't sufficient space in this paper to provide background information. To this end the reader is referred to [19] and [20] as good sources for general information on these topics. The whitepaper entitled An Illustration of the benefits of MIPS RI2000 and OCTANE System Architecture, [21], also provides some background information on microprocessor architecture and is also referenced in the sub-section below discussing differences between MIPS RI0000 and MIPS RI2000.

### Description and Comparison of MIPS R5000 and QED RM5200

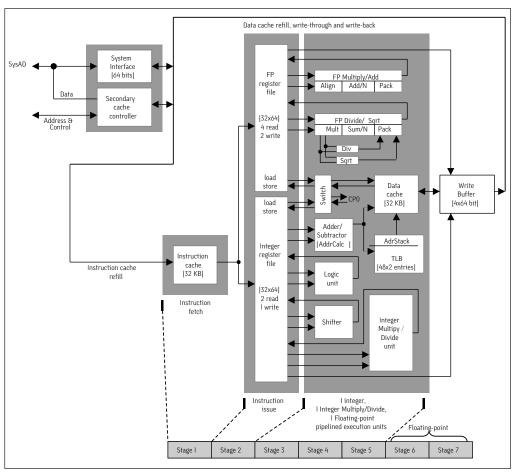

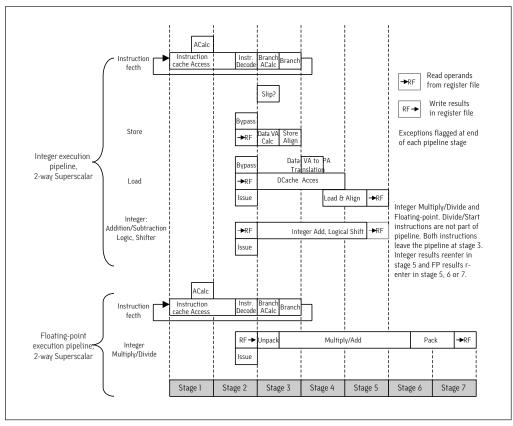

Figure 14a details the QED RM5200 architecture and pipeline respectively.

Figure 14a, QED RM5200 Architecture.

Figure 14b, QED RM5200 Pipeline.

Both MIPS R5000 and QED RM5200 have a 32KB primary instruction and a 32KB primary data cache. Both primary caches are on-chip and are two way set-associative. The secondary cache is external, or off-chip, and is also two way set-associative with sizes of 512 KB, 1 MB and 2 MB. On O2, both MIPS R5000 and QED RM5200 have a 1 MB secondary cache. Two way set-associativity offers a good solution to the trade-off between chip complexity and maximizing re-use of cached data, which in turn benefits application performance.

Both MIPS R5000 and QED RM5200 perform secondary cache data writes over the SysAD, or system bus. Secondary cache addresses, as well as some control data, have a separate bus. The motivating factor for this design feature is to reduce chip complexity, and therefore size and cost, by simplifying the secondary cache controller design. Since applications tend to noticeably miss secondary cache, sharing the SysAD bus with secondary cache data may potentially compromise system performance due to increased bus contention. Separating the addresses and control data away from the SysAD bus, however, allows overall application performance to be maintained while retaining the benefits of reduced complexity and costs.

The system interface of both MIPS R5000 and QED RM5200 are non-overlapping. This means that only one outstanding request is allowed, and this request

must be serviced before another can be issued. Since this could affect secondary data cache transfers, and hence application performance, both microprocessors also buffer external main memory writes in a buffer that can store four 64-bit data and address pairs. This allows the processor to continue executing after issuing a memory update and typically improves application performance. During uncached write-through stores, the write buffer increases performance by de-coupling SysAD bus transfers from the instruction execution stream. Again this will yield improvements in application performance.

One of the key differences between the MIPS R5000 and the QED RM5200 is the supported clock rates. As is common on most modern microprocessors, both QED RM5200 and MIPS R5000 use Phase-Locked Loop [PLL] circuitry to multiply an externally supplied clock signal. For MIPS R5000 the maximum speed of the external clock signal and the multipliers to generate the internal clock rate are restricted to 2, 3 and 4 and as a result the maximum internal clock rate of MIPS R5000 is 200 MHz. On QED RM5200 the range of clock signal multipliers is expanded to 2, 2.5, 3, 3.5, 4, 4.5, 5, 6, 7, 8 and 9 which clearly yields a greater range of internal versus external clock speeds. This in turn allows more flexibility when incorporating QED RM5200 into 02 and ultimately facilitates a better match with user application performance requirements.

For both MIPS R5000 and QED RM5200 the SysAD speed NO2 is set to 100 MHz. Given the greater flexibility in internal clock rate on QED RM5200 this may appear as a limitation. It isn't so. The significant primary and secondary cache sizes, coupled with the performance advantage afforded through the write buffer, have shown the 100 MHz maximum SysAD bus speed not to be a limiting factor.

The Translation Look-aside Buffer [TLB] on both MIPS R5000 and QED RM5200 applies to both data and instructions and hence is referred to as the Joint TLB [JTLB]. On both microprocessors it is direct mapped and hence accommodates varying page sizes between 4 KB and 16 MB on a per page basis. Being able to adjust page size allows increased flexibility in meeting the system requirements imposed through running many varied applications.

The JTLB can store 96 page translations organized as 48 dual entries. Organizing the JTLB in this fashion significantly reduces the area on the microprocessor chip dedicated to the TLB, and hence saves both in chip area and overall power consumption. Since nearly every instruction executed by the microprocessor typically incurs a page translation, maximizing the size of the table to 96 overall entries will improve application performance by allowing more data and instruction page translations to be cached in the JTLB and thereby avoiding expensive memory accesses. On RM5200 there is also a 2-entry Instruction TLB (ITLB) and a 4-entry Data TLB (DTLB). These further improve application performance since when an instruction and data page translations hit both the ITLB and DTLB simultaneously, both data and instruction address translations can occur in parallel. If such translations should miss either the ITLB or DTLB. they are both transparently filled from the JTLB.

Both MIPS R5000 and QED RM5200 implement a 5-stage integer pipeline and 7-stage floating-point pipeline. Both the integer and floating-point execution units incorporate individual instruction fetch logic and consequently they are both dual issue, allowing one floating-point instruction and one integer instruction to be issued per cycle. Clearly for codes that contain an even mix of floating point and integer instructions this greatly assists application performance.

The integer unit includes: an adder/subtractor execution unit, which also calculates addresses; a logic execution unit; a shift execution unit, as well as a separate integer multiply/divide unit. Even though the integer multiply/divide unit has a longer latency compared with the other units, once an instruction is issued to it, subsequent instructions can be issued to the other units and thereby the longer latency has little direct impact on overall execution. In a similar way, the floating-point unit is divided into: a multiply/add unit, and a divide/square root unit. Although the latency of the divide/square root unit is again longer than that of the integer queue, once an

instruction is scheduled to it the processor can then schedule subsequent instructions to the multiply/add unit. As a consequence the longer latency has less effect on overall throughput and application performance. There are 32 general purpose integer and 32 floating-point registers on both MIPS R5000 and QED RM5200. Registers are where the operands associated with instructions are stored while they are executing on the microprocessor. Having more will clearly allow more instructions to be executing in the microprocessor at one time, however, this needs to be balanced with other features of the processor, such as the number of instructions that can simultaneously execute, as well as the number of outstanding memory accesses etc. For both MIPS R5000 and QED RM5200 32 integer and 32 floating point registers were found to be suitable for the overall design of the microprocessors. Both MIPS R5000 and QED RM5200 also have two special purpose 64-bit registers for the integer multiply/divide execution unit. These special purpose registers facilitate two instructions beyond the MIPS IV ISA instruction set, viz. integer multiplyaccumulate and three operand integer multiply, however, both these instructions are primarily targeted at the embedded processor market and hence are not utilized by typical O2 applications.

As mentioned above, since secondary cache data transfers share the SysAD bus with memory accesses this could potentially yield an increase in bus traffic and contention, impacting application performance. By default, therefore, both MIPS R5000 and QED RM5200 use a write-back cache protocol to reduce system bus traffic and eliminate potential delays waiting for memory accesses. In some situations, however, it is desirable to change the cache protocol since caching is undesirable and may in fact cause an overhead to overall throughput. One such example relevant to 02 is when addressing screen buffer data. To support this both MIPS R5000 and QED RM5200 offer write-through protocols which can be selected by software on a per-page basis.

The four types of protocol supported by MIPS R5000 and QED RM5200 are defined as follows:

- uncached: Sections of memory using an uncached protocol will not access cache during reads and will not update the cache during writes.

- 2. write-back: When reading data, viz. load operations and instruction fetches, a write-back protocol will search each cache level in turn. If no hits occur the data will be fetched from main memory. For writes, i.e. store operations, each cache level is checked to see if the location is included in a cache line. If a hit occurs the location is updated and data is written to main memory and the cache line marked dirty. If no hits occur in cache then the cache line is loaded from memory and then written with no update to cache.

- 3. write-through with write allocate: Using this protocol reads will search the primary cache and go to main memory if the data is found not to be resident. Using a write-through protocol, data is not stored in secondary cache. On data writes, again the primary cache is searched and if the location is found to be resident, the value is updated both in primary cache and main memory and the write-back bit of the cache line is also left unchanged. No writes occur to the secondary cache. If the data is not resident then the cache line is loaded from memory into primary cache, updated and written back with no update to secondary cache.

- 4. write-through without write allocate: This protocol is the same as the write-through with write allocate protocol except that when writing data, if the data is not resident in primary cache then the value is read in and written back to memory without loading the data into primary cache.

The four cache protocol alternatives allow significantly increased flexibility when designing a system such as O2 so that it can meet the demands of many varied applications. The use of main memory for the frame buffer and texture memory places significantly diff-

erent requirements on a system to obtain maximum performance compared with say an application that generates rendered images. Being able to choose the appropriate cache protocol avoids un-necessary transfers over the SysAD bus traffic thereby reducing contention, processor delays etc. and maximizing application performance. Furthermore, since the write-through cache protocol can be individually set for each page translation stored in the JTLB and DTLB and each entry in the ITLB and DTLB can accommodate different page sizes, one JTLB entry, say, can potentially accommodate an entire frame buffer. Clearly compared with fixed page size JTLB and DTLB entries this frees up many entries which can be utilized by other executing codes. This in turn helps to maximize overall application performance and throughput, which is of obvious benefit to the end user.

The information in this subsection is intended to be a summary of the MIPS R5000 and QED RM5200 architectures and the key differences. Inevitably some aspects of both architectures don't receive as much information as perhaps they should, so to that end [22] and [23] provide more details on both microprocessors.

### Description and Comparison of MIPS R10000 and MIPS R12000

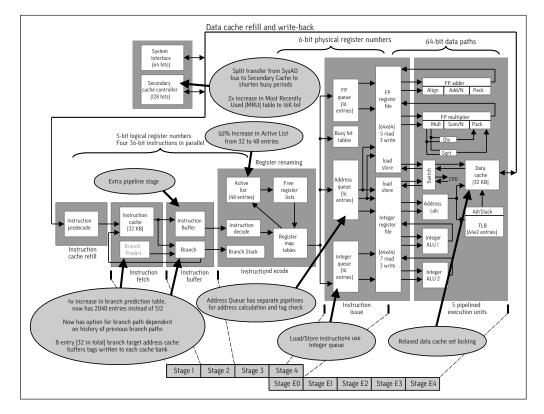

Figure I5a and I5b show the MIPS RI2000 architecture and pipeline respectively, highlighting key differences relative to MIPS RI0000.

Figure 15a and 15b, MIPS R12000 Architecture and Pipeline showing key differences relative to MIPS R10000.

As can be seen from Figure 15 there are several changes when comparing MIPS R10000 and MIPS R12000 and a full description of all of these is provided in [21]. Due to the nature of how the CPU is utilized for graphics in O2's architecture some of these changes will exhibit more influence and those will be briefly discussed here. Like the change from MIPS R5000 to QED RM5200 the secondary cache size is also constant between MIPS R10000 and MIPS R12000 on O2 and hence any performance improvements are a direct result of processor architecture as well as clock speed differences.

Like in OCTANE, the increased active list in MIPS RI2000 in O2 will allow more instructions to be executing or pending execution. The resulting increase in speculatively executed instructions will improve application performance. A further benefit on O2 is that since secondary cache transfers share the SysAD bus, an increased active list accommodates more pending load/store operations and hence is likely to help prevent processor stalls when bus traffic is high.

As mentioned in [21] most large application codes exhibit a significant number of branch instructions, sometimes even up to 15-20% of all the instructions. Stalling the processor pipeline as a result of a mis-predicted branch incurs a very significant penalty and hence a 4x increase in the branch prediction table is

likely to yield a very significant improvement application performance. The incorporation of a branch target address cache, which significantly reduces the time taken to obtain a branch address, will add to these benefits. Graphics libraries typically include a significant number of branch instructions to accommodate varying state within applications and as a consequence the increase branch prediction table length will significantly help. During dynamic graphics instructions are also repeated many times and hence the locality of reference is typically higher. As a result the branch target address cache will also noticeably improve performance.

Although the secondary cache address and control signals are separated from the SysAD bus in O2's architecture, the results of such searches are still transferred across the SysAD bus. As a consequence correct way prediction will slightly decrease this traffic and hence potentially improve performance through reduced bus contention. As shown in [21] the increase in MRU table in MIPS R12000 noticeably reduces the number of mis-predicted branches. Integrated into the architecture this change will typically reduce the contention on the SysAD bus and hence offer performance benefits beyond the direct reduction in time spent checking secondary cache.

Like the previous sub-section, this sub-section is intended to be a very brief summary of the differences between MIPS R10000 and MIPS R12000. As mentioned above [21] discusses these details in significantly more detail. Further details and information on both microprocessors are given in [24] and [25].

### Summary of Differences between QED RM5200 and MIPS R12000

The previous two subsections presented a summary of the differences between the new and the previous processors in both families offered in O2 systems. This section highlights some of the more significant differences between the two microprocessor family architectures in more detail, explaining the motivations and reasons behind them and how they translate into the positioning of O2 systems.

MIPS R12000 instruction fetch and decode unit allow four instructions to be decoded and scheduled per cycle which allows the five execution units to be kept as busy as possible. Such features, while significantly adding to the throughput of the processor for many applications, do increase the size, complexity and cost. Some applications such as video processing, however, typically yield many similar instructions, such as memory read and writes, and hence by their nature don't take full advantage of the sophisticated features of MIPS R12000. For such applications, even though QED RM5200 replicates the instruction fetch and decode in both the integer and floating point queues, and hence only allows a maximum of two instructions to be executed per cycle, the overall system performance is very high. To a user this is made even more attractive by the significantly lower overall system cost. As a consequence, previously MIPS R5000 and now QED RM5200 based 02 systems offer very powerful system for applications oriented towards video at low cost. Such applications clearly allowing full advantage to be taken the sophisticated features afforded by 02's unique arechitecture.

Likewise, for computationally intensive applications MIPS R12000 incorporates out of order execution to minimize the effects of waiting for memory accesses as well as other reasons. QED RM5200 does not include this technology but again this also significantly simplifies its design and lowers the overall cost.

The same applies to other advanced MIPS RI2000 eatures such as branch prediction. In terms of positioning MIPS RI2000 and QED RM5200 O2 systems, therefore, the features of MIPS RI2000 such as out of order execution and branch prediction can yield significantly improvements to overall system throughput for applications that are more computationally intensive. From a user perspective, though, these improvements need to be balanced with overall system cost.

In a similar way the MIPS R12000 employs an MRU table to predict which way of the secondary cache is searched first and this can significantly reduce the time taken to check if data is resident in secondary cache. Since most applications typically exhibit a large number of secondary cache accesses this can be very beneficial. QED RM5200 doesn't implement a MRU table and relative to MIPS R12000, this may yield a slight overhead during secondary cache searches. With real world applications, however, many other factors can affect overall system performance. Again from a user perspective, therefore, the specific application[s] being used will determine the tradeoff between potentially higher computational performance of MIPS R12000 based 02 systems versus the cost advantages of the QED RM5200 based 02 systems.

Similar reasoning applies to comparisons between features such as the number of registers on MIPS R12000 compared with QED RM5200. Since MIPS RI2000 has 64 integer and 64 floating point registers compared with 32 integer and 32 floating-point registers on QED RM5200, it may appear that MIPS R12000 will have a significant advantage. - a greater number of registers allows a greater number of instructions to be executing in the processor. While this is true in principle, the effect it has on application performance will be very dependent on many other factors. These factors include the distribution of instructions between load/store, integer or floating point instruction which is very application specific, as well as other factors arising from specific features of the microprocessor design, such as how many instructions can be scheduled in one cycle etc. etc. As a consequence the price performance advantages of QED RM5200 based systems compared with higher potential computational capabilities of MIPS R12000 have to be balanced. In areas such as video processing the QED RM5200 based 02 systems offer very attractive solutions.

### An Illustration of the Synergy between 02's CPU and Architecture for graphics.

Most applications that are well suited to 02's architecture yield a substantial element of graphics activity and even though the specifics of each application may vary, typically graphics activities translate to drawing lower level graphics primitives such triangles or lines. This section explains how MIPS RI2000 and QED RM5200 combined with 02's architecture demonstrate significant benefits in graphics primitive performance. How this translates to application performance is covered by the next section, Translation of Improvements Afforded Through New CPUs into End User Benefits.

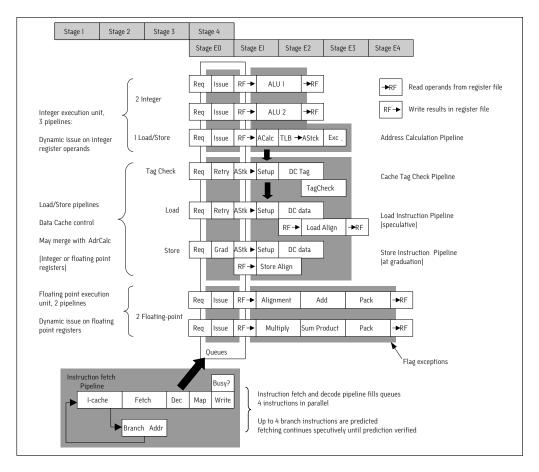

Figure 16 shows a schematic diagram of the OpenGL pipeline and how it maps to the key components of O2's architecture.

Figure 16 Diagram of OpenGL pipeline and how it maps to the key components of O2 architecture.

As shown in Figure 16, 02's architecture uses the CPU for several stages in the OpenGL pipeline. Vertex data, comprising vertices, normals and colors, are either individually stored in main memory or within vertex arrays and display lists. Viewing and projection matrix transformations as well as view volume clipping and triangle setup are performed on the CPU. Subsequent primitive data, such as lines, triangles etc., are sent to the MRE which completes the rasterization process, performs depth buffering and other pixel based tests. Finally the pixel data is stored in the frame buffer which as mentioned earlier, is a dedicated section of main memory. In the case of textures, depending on the packing format, e.g. RGB, RGBA etc., dictates whether they will be unpacked by the CPU and subsequently pushed to the MRE or whether they will pulled directly from main memory by the MRE.

Since the CPU is such an integral part of 02 graphics, one would expect in most cases an increase in CPU performance to lead to a corresponding improvement in graphics performance. Table I shows the performance improvements afforded through QED RM5200 and MIPS RI2000, relative to MIPS R5000 and MIPS RI0000 respectively, for Triangle fill rate and texture downloads. The relative improvements for clock rate, SPECint95 and SPECfp95 increases are also given for comparison.

|                                                                                                     | Performance of QED RM5200 compared with MIPS R5000 |   | Performance of MIPS R12000<br>compared with MIPS R10000 |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|---|---------------------------------------------------------|

| Triangle fill rate [Triangles/s]<br>[Gouraud shaded, Z-buffered,<br>I infinite light]               |                                                    | · |                                                         |

| 1 Pixel                                                                                             | 1.57x                                              |   | 1.26x                                                   |

| 25 Pixel                                                                                            | 1.58x                                              |   | 1.22x                                                   |

| 50 Pixel                                                                                            | 1.38x                                              |   | 1.01x                                                   |

| Triangle fill rate [Triangles/s]<br>[Gouraud shaded, Textured,<br>I infinite light]                 |                                                    |   |                                                         |

| 1 Pixel                                                                                             | 1.47x                                              |   | 1.30x                                                   |

| 25 Pixel                                                                                            | 1.47x                                              |   | 1.31x                                                   |

| 50 Pixel                                                                                            | 1.47x                                              |   | 1.15x                                                   |

| Texture Image Downloads<br>[Images loaded/s]<br>[64x64, Unsigned byte,<br>mip-mapped, no primitive] |                                                    |   |                                                         |

| RGB                                                                                                 | 1.41x                                              |   | 1.34x                                                   |

| RGBA                                                                                                | 1.42x                                              |   | 1.24x                                                   |

| Clock Speed                                                                                         | 1.50x                                              |   | 1.20x                                                   |

| SPECint95                                                                                           | 1.49x                                              |   | 1.20x                                                   |

| SPECfp95                                                                                            | 1.16x                                              |   | 1.07x                                                   |

Table I, triangle fill rate and texture image download performance improvements afforded by QED RM5200 and MIPS R12000 relative to MIPS R5000 and MIPS R10000.

Most readers are probably familiar with the fact that objects drawn in three dimensions on a computer screen are typically represented by triangles. The triangle fill rate results shown in Table I measure the speed with which triangles can be sent to the screen after performing additional operations, such as z-buffering and lighting. The two triangle fill-rate cases shown present results for gouraud shaded, z-buffered, one infinite light and gouraud shaded, one infinite light, 64x64 trilinear modulated textue cases.

The size with which a triangle appears on the screen clearly affects the number of pixels sent to the frame buffer and hence affects the speed with which a triangle is drawn. When fewer pixels are drawn the time taken to calculate and send pixels to the frame buffer is reduced relative to performing the geometric transformations on the vertices and normals. In cases where triangle's screen area is very small, say less than I pixel, the overall time taken to draw a triangle is typically dominated by the geometry calculations. Such cases are referred to as a geometry limited. In cases where individual triangles result in many screen pixels, and may also be textured, then the time taken to draw an individual triangle is typically dominated by the time taken to create individual pixels and send them to the frame-buffer. Such cases are referred to as fill limited. In real life the number of pixels within a triangle is very dependent on both model view point and orientation. In the results above, one pixel, 25 pixel and 50 pixel triangles are included to give an indication of performance over a range of different view-points and orientations.

The texture image download tests measure the speed with which texture images can be transferred from memory to the graphics. On O2, because main mem-ory is used for both texture memory and the frame buffer, the path taken by data is slightly different compared with other more traditional graphics architectures, such as SUN Creator3D. On these architectures both texture and frame buffer memory are both located on the graphics subsystem. Many readers are also probably aware that there are many different formats by which image data used for textures can be stored which affects the accuracy and number of bytes used to store the red, green and blue components and also whether the image includes transparency or not. The RGBA format guoted above is typically used by many applications that utilize texturing. The RGB format has also been included since it uses the CPU to unpack the image data before the texture is sent to the MRE engine and hence the CPU has more potential to influence performance.

The rest of this section describes how the CPU influences O2 system performance for each of the above tests, however, it is worth briefly mentioning the method used to gather the necessary data.

Both MIPS R10000 and MIPS R12000 include performance counters which can be used to measure internal performance. These counters measure metrics such as cache misses, mis-predicted branches, instructions executed etc. and provide insight into the parts of the processor stressed by executing code. Unfortunately due to their simpler design, neither MIPS R5000 nor

QED RM5200 include such performance counters and hence the examples provided below do not include examples for these processors. It is likely that some of the results described for MIPS RI2000 will carry across to QED RM5200 although due to the microprocessor architectural differences many will not.

In [21] the benefits afforded through the architectural improvements of MIPS R12000 relative to MIPS R10000 are demonstrated through an example using the CATIA SolidE function. For this example the CPU time during this test was almost exclusively devoted to the application code, CATIA. The graphics tests used to generate the results shown in Table I use and application specifically designed to stress aspects of a system's graphics performance. Consequently this typically results in a significantly greater amount of CPU time spent executing system library code. This is particularly true for O2 since the CPU is utilized for many of the graphics functions. Unlike application code, system libraries typically contain many sections of code that are dependent on a specific processor type, including both MIPS R10000 and MIPS R12000. Whereas [21] demonstrated the influence of MIPS R12000 architecture improvements by showing the differences in recorded processor counter values, a similar approach for the graphics tests given above would be less appropriate due to the significantly greater influence of processor dependent code. To that end, higher-level statistics such as graduated instructions per cycle are more appropriate and have been used below, however, even then it should be remembered that any differences in code do not allow exact comparisons between architectures.

### Triangle fill-rate

Figure 17a shows an extract of OpenGL pseudo code taken from the triangle fill rate test. It purposely doesn't contain all the code executed during the test, however, is intended to represent the key elements of the test.

```

glEnable[ GL_DEPTH_TEST ];

glEnable[ GL_LIGHTO ];

glShadeModel[ GL_SMOOTH ];

```

```

START LOOP

glBegin( GL_TRIANGLE_STRIP );

glNormal3fv[-0.695387, -0.695387, 0.181309 ];

glVertex3fv[-3.43724, -3.99015, -5.89054];

glNormal3fv[-0.695359, -0.705928, 0.134688];

glVertex3fv[-3.45947, -4.0145, -5.87967];

glNormal3fv[-0.684835, -0.69964, 0.203727];

glVertex3fv[-3.41042, -4.00736, -5.85063];

glNormal3fv[-0.674367, -0.703943, 0.222919];

glNormal3fv[-0.450128, -0.16489, 0.877608];

glVertex3fv[-1.4386, -2.75375, -4.98767];

glNormal3fv[-0.449494, -0.176747, 0.875623];

glVertex3fv[-1.45689, -2.77448, -4.9768];

glNormal3fv[ -0.458765, -0.178623, 0.870419];

glVertex3fv[-1.47405, -2.76471, -4.98318];

glEnd[]:

END LOOP

```

Figure 17a OpenGL pseudo code during triangle fill rate test.

The first three lines show the settings enabling gouraud shading, z-buffering, lighting. During the test, triangles are sent to the graphics as triangle strips, comprising 120 triangles per strip and 10 strips overall. The vertices and normals sent are generated from random numbers and stored before the test measurement commences. During the test the triangle strips are repeatedly drawn for a period of 10 seconds and then based on the time taken and the total number of triangles the triangles drawn per second is calculated.

As the triangle fill rate results in Table I show, the percentage speed for both RM5200 and MIPS R12000 is significantly greater than clock rate for both one and 25 pixel cases. This may seem as though we are getting something for nothing, however, being able to perform geometric calculations faster and better cache re-use, especially in view of the use of the SysAD bus for cache data transfer, is likely to yield this result. As the triangle size increases to 50 pixels, fill limitations become more noticeable and while the QED RM5200 still shows reasonable improvement, the MIPS R12000 yields little speed up.

Table 2 shows graduated instructions/cycle, graduated floating point instructions/cycle and graduated load store instructions per cycle.

|                                                 | MIPS R10000 250 MHz | MIPS R12000 300 MHz |

|-------------------------------------------------|---------------------|---------------------|

| Graduated instructions per cycle                |                     |                     |

| 1 Pixel                                         | 1.220049            | 1.293745            |

| 25 Pixel                                        | 1.243763            | 1.302638            |

| 50 Pixel                                        | 1.206619            | 1.311304            |

| Graduated floating point instructions per cycle |                     |                     |

| l Pixel                                         | 0.344053            | 0.379708            |

| 25 Pixel                                        | 0.353285            | 0.386848            |

| 50 Pixel                                        | 0.341924            | 0.394801            |

| Graduated load/store instructions per cycle     |                     |                     |

| l Pixel                                         | 0.458965            | 0.493239            |

| 25 Pixel                                        | 0.467848            | 0.504176            |

| 50 Pixel                                        | 0.456738            | 0.498432            |

Table 2, graduated instructions per cycle, graduated floating point instructions per cycle and graduated load store instructions per cycle.

Graduated instructions per cycle, including floating point and load/store instructions, represent the throughput of the processor and hence provide a measure of how well the processor is able to execute code. Many of the architectural improvements in the MIPS RI2000 are specifically intended to improve the processor's ability to execute instructions: The increased active list allows more instructions to be executing or pending execution as well as increasing speculation. The increased branch prediction table typically yields better branch prediction and hence leads to fewer flushes of the execution pipeline. The increased MRU table typically yields fewer delays when data is resident in secondary cache and hence allows the processor to be fed with more instructions. As can be seen from Table 2, the graduated instructions, graduated floating point instructions and graduated load store instructions observed during the triangle fill-rate test all increase for the one, 25 and 50 pixel triangle cases, showing that the architectural modifications do indeed yield the desired results.

|                       | MIPS RI0000 250 MHz | MIPS R12000 300 MHz |

|-----------------------|---------------------|---------------------|

| L1-L2 bandwidth       |                     |                     |

| l Pixel               | 12.94796            | 16.53812            |

| 25 Pixel              | 14.36574            | 18.06257            |

| 50 Pixel              | 17.85962            | 22.61384            |

| Memorγ bandwidth used |                     |                     |

| 1 Pixel               | 1.622079            | 2.04869             |

| 25 Pixel              | 1.689756            | 2.108009            |

| 50 Pixel              | 1.805317            | 2.227033            |

| Average MFLOPS        |                     |                     |

| 1 Pixel               | 88.4582             | 106.545             |

| 25 Pixel              | 87.57669            | 111.4861            |

| 50 Pixel              | 85.48092            | 118.4403            |

|                       |                     |                     |

Table 3, shows the L1-L2 bandwidth used, memory-bandwidth used and Average MFLOPS seen during the test.

The L1-L2 bandwidth represents the amount of data transferred between the primary and secondary caches during the execution of a program. It is defined by combining the number of bytes transferred from secondary cache to primary cache with the number of bytes written back from primary cache to secondary cache and dividing the total by the overall execution time. Since MIPS RI2000 uses a write back cache protocol, it represents how well primary cache misses are being satisfied from secondary cache. Since secondary cache misses will cause memory access, an increase in the L1-L2 bandwidth is beneficial to code execution. The increased MRU table on MIPS RI2000 typically reduces the time taken when a data location is in secondary cache and hence is likely to result in an improvement in L1-L2 bandwidth. Likewise, increasing the graduated load/store instructions per cycle is also likely to improve the L1-L2 bandwidth.

In a similar way, the memory bandwidth used represents the amount of data transferred between secondary cache and main memory. It is defined by combining the number of bytes transferred from main memory to secondary cache with the number of bytes written back from secondary cache and dividing the total by the overall execution time. An increase in the bandwidth typically demonstrates that the microprocessor is being more efficient since it shows that more data is flowing into and out of the processor during execution. Again increases in all graduated instructions, but especially load/store instructions, would be expected to yield an increase in memory bandwidth used.

MFLOPS, Millions of floating point instructions, represents the graduated floating-point instructions divided by the overall execution time and is often used as a measure of computing power. An increase in MFLOPS demonstrates that more floating-point instructions are being performed in the same time. An increase in graduated floating point instructions per cycle would typically be linked with an increase in MFLOPS.

As can be seen from the results shown in Table 3, the architectural features of MIPS RI2000 yield increases in both the observed LI-L2 and memory bandwidth used along with the MFLOPS during the triangle fill-rate tests

### Textured Triangle fill-rate